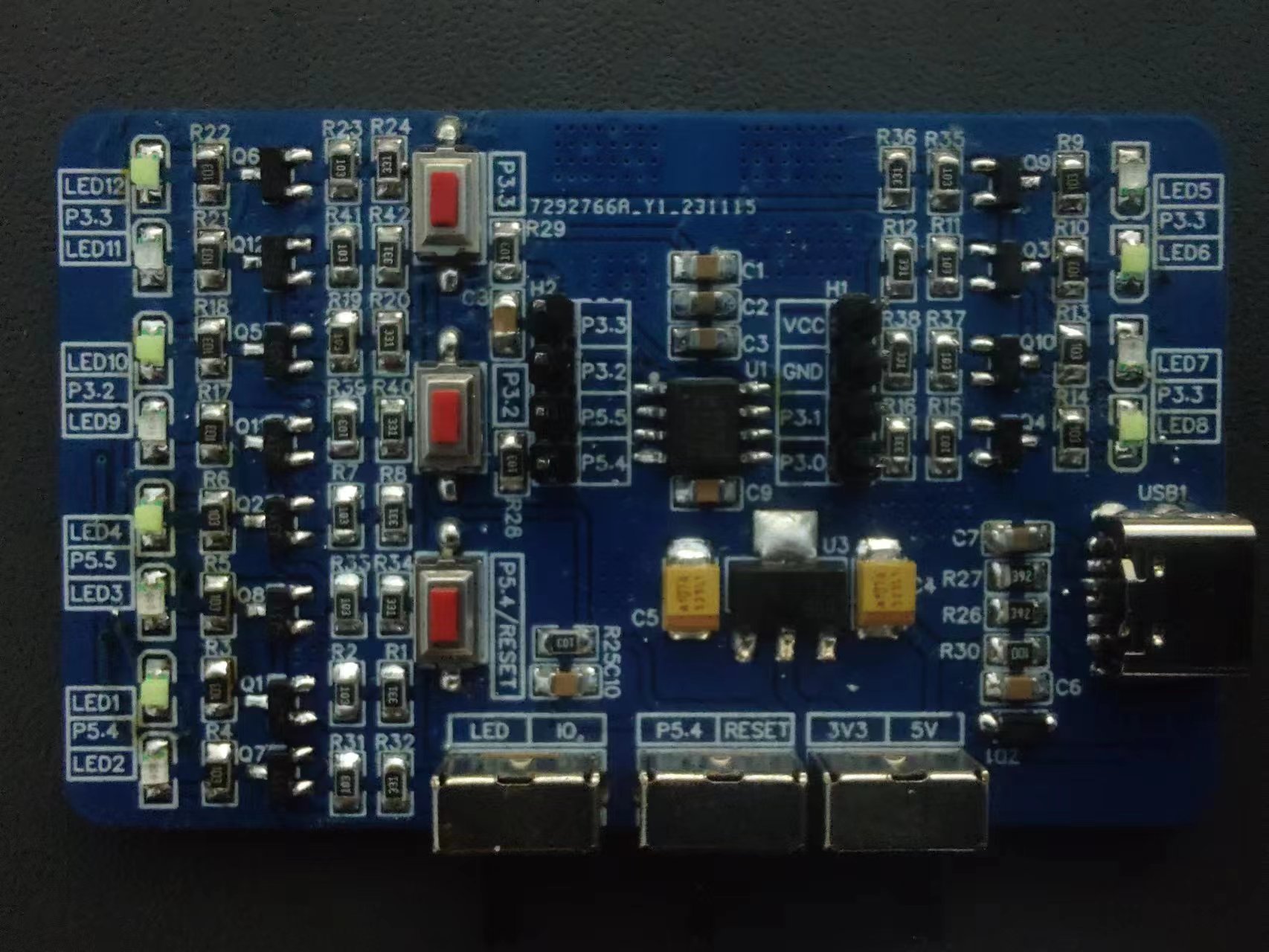

焊接练习板

简介

一个基于STC8G1K08-8PIN的焊接练习板

简介:一个基于STC8G1K08-8PIN的焊接练习板开源协议

:LGPL 3.0

(未经作者授权,禁止转载)描述

未经允许,严禁商用!!!

- LGPL 3.0

- 禁止用于商业和复刻者售卖

本工程基于STC8G1K08-8PIN

功能介绍

- IO直接引出

- 3个开关可选择模式 LED/IO口模式 、 P5.4/RESET模式 、 3V3/5V模式

- 有3个引出开关--1RESET-2普通按键

- 下载口在一侧-方便下载

二、芯片简介

内核• 超高速 8051 内核(1T),比传统 8051 约快 12 倍以上•指令代码完全兼容传统8051• 16 个中断源,4 级中断优先级• 支持在线仿真工作电压• 1.9V~5.5V• 内建LDO工作温度• -40℃~85℃Flash 存储器• 最大 17K 字节 FLASH 空间,用于存储用户代码• 支持用户配置 EEPROM 大小,512 字节单页擦除,擦写次数可达10万次以上• 支持在系统编程方式(ISP)更新用户应用程序,无需专用编程器• 支持单芯片仿真,无需专用仿真器,理论断点个数无限制SRAM• 128 字节内部直接访问 RAM(DATA)• 128 字节内部间接访问 RAM(IDATA)• 1024 字节内部扩展 RAM(内部 XDATA)时钟控制• 内部高精度IRC(4MHz~36MHz,ISP 编程时可进行上下调整,还可以用户软件分频到较低的频率工作, 如100KHz)– 误差±0.3%(常温下 25℃)– -1.38%~+1.42%温漂(全温度范围,-40℃~85℃)– -0.88%~+1.05%温漂(温度范围,-20℃~65℃)• 内部 32KHz 低速 IRC(误差较大)• 外部晶振(4MHz~36MHz)和外部时钟复位• 硬件复位• 上电复位(在芯片未使能低压复位功能时有效)• 复位脚复位。出厂时P5.4 默认为I/O 口,ISP 下载时可将P5.4 管脚设置为复位脚(注意:当设置P5.4 管脚为复位脚时,复位电平为低电平)• 看门狗溢出复位• 低压检测复位,提供 4 级低压检测电压::2.0V、2.4V、2.7V、3.0V• 软件复位• 软件方式写复位触发寄存器中断• 提供16 个中断源:INT0(支持上升沿和下降沿中断)、INT1(支持上升沿和下降沿中断)、INT2(只支 持下降沿中断)、INT3(只支持下降沿中断)、INT4(只支持下降沿中断)、定时器0、定时器1、定时 器2、串口1、串口2、ADC 模数转换、LVD 低压检测、SPI、I2C、比较器、PCA/CCP/PWM• 提供 4 级中断优先级• 时钟停振模式下可以唤醒的中断:INT0(P3.2)、INT1(P3.3)、INT2(P3.6)、INT3(P3.7)、INT4(P3.0)、T0(P3.4)、 T1(P3.5)、T2(P1.2)、RXD(P3.0/P3.6/P1.6)、RXD2(P1.0)、CCP0(P1.1/P3.5)、CCP1(P1.0/P3.6)、CCP2(P3.7)、 I2C_SDA(P1.4/P3.3)以及比较器中断、低压检测中断、掉电唤醒定时器唤醒数字外设• 3个 16 位定时器:定时器 0、定时器 1、定时器 2,其中定时器 0 的模式 3 具有 NMI(不可屏蔽中断)功能,定时器 0和定时器 1 的模式 0 为 16 位自动重载模式• 2个高速串口:串口 1、串口 2,波特率时钟源最快可为 FOSC/4• 3组16位PCA模块:CCP0、CCP1、CCP2,可用于捕获、高速脉冲输出,及6/7/8/10位的PWM输出• SPI:支持主机模式和从机模式以及主机/从机自动切换• I2C:支持主机模式和从机模式模拟外设• 超高速ADC,支持10位精度15通道(通道0~通道14)的模数转换• ADC的通道15用于测试内部参考电压(芯片在出厂时,内部参考电压调整为1.19V,误差±1%)• 比较器,一组比较器(比较器的正端可选择CMP+端口和所有的ADC 输入端口,所以比较器可当作多路 比较器进行分时复用)• DAC:3 路PCA/CCP/PWM 可当3 路DAC 使用GPIO• 最多可达 18 个 GPIO: P1.0~P1.7、P3.0~P3.7、P5.4~P5.5• 所有的 GPIO 均支持如下 4 种模式:准双向口模式、强推挽输出模式、开漏输出模式、高阻输入模式• 除P3.0和P3.1外,其余所有I/O口上电后的状态均为高阻输入状态,用户在使用I/O口时必须先设置I/O口模式• 另外每个I/O均可独立使能内部4K上拉电阻

三、工程展示

以下全是shi山有能力可以自己打

设计图

未生成预览图,请在编辑器重新保存一次

未生成预览图,请在编辑器重新保存一次BOM

暂无BOM

暂无BOM 克隆工程

克隆工程知识产权声明&复刻说明

本项目为开源硬件项目,其相关的知识产权归创作者所有。创作者在本平台上传该硬件项目仅供平台用户用于学习交流及研究,不包括任何商业性使用,请勿用于商业售卖或其他盈利性的用途;如您认为本项目涉嫌侵犯了您的相关权益,请点击上方“侵权投诉”按钮,我们将按照嘉立创《侵权投诉与申诉规则》进行处理。

请在进行项目复刻时自行验证电路的可行性,并自行辨别该项目是否对您适用。您对复刻项目的任何后果负责,无论何种情况,本平台将不对您在复刻项目时,遇到的任何因开源项目电路设计问题所导致的直接、间接等损害负责。

评论