FPGA 100M采样率 示波器

简介

使用FPGA制作示波器,采用verilog编写,没用软核。采样率最高100Mhz。垂直档位有10mv~10v/div。可光标测量,有频率计,可调触发电压、触发模式、触发边缘,可上下平移,可调耦合方式。

简介:使用FPGA制作示波器,采用verilog编写,没用软核。采样率最高100Mhz。垂直档位有10mv~10v/div。可光标测量,有频率计,可调触发电压、触发模式、触发边缘,可上下平移,可调耦合方式。开源协议

:GPL 3.0

(未经作者授权,禁止转载)描述

本示波器采用FPGA+波形调理电路的架构实现。采用FPGA的好处是可以高速地进行数据采集和处理,但UI画面绘制较难,所以本示波器的UI方面比较难看。学习制作一个示波器,可以很大程度地提高Verilog水平,同时也可以提高模拟电路设计水平。由于示波器需要测量小信号,所以在布板时要考虑电磁兼容,否则会有干扰引入,导致波形毛刺。

下面进行硬件原理介绍。

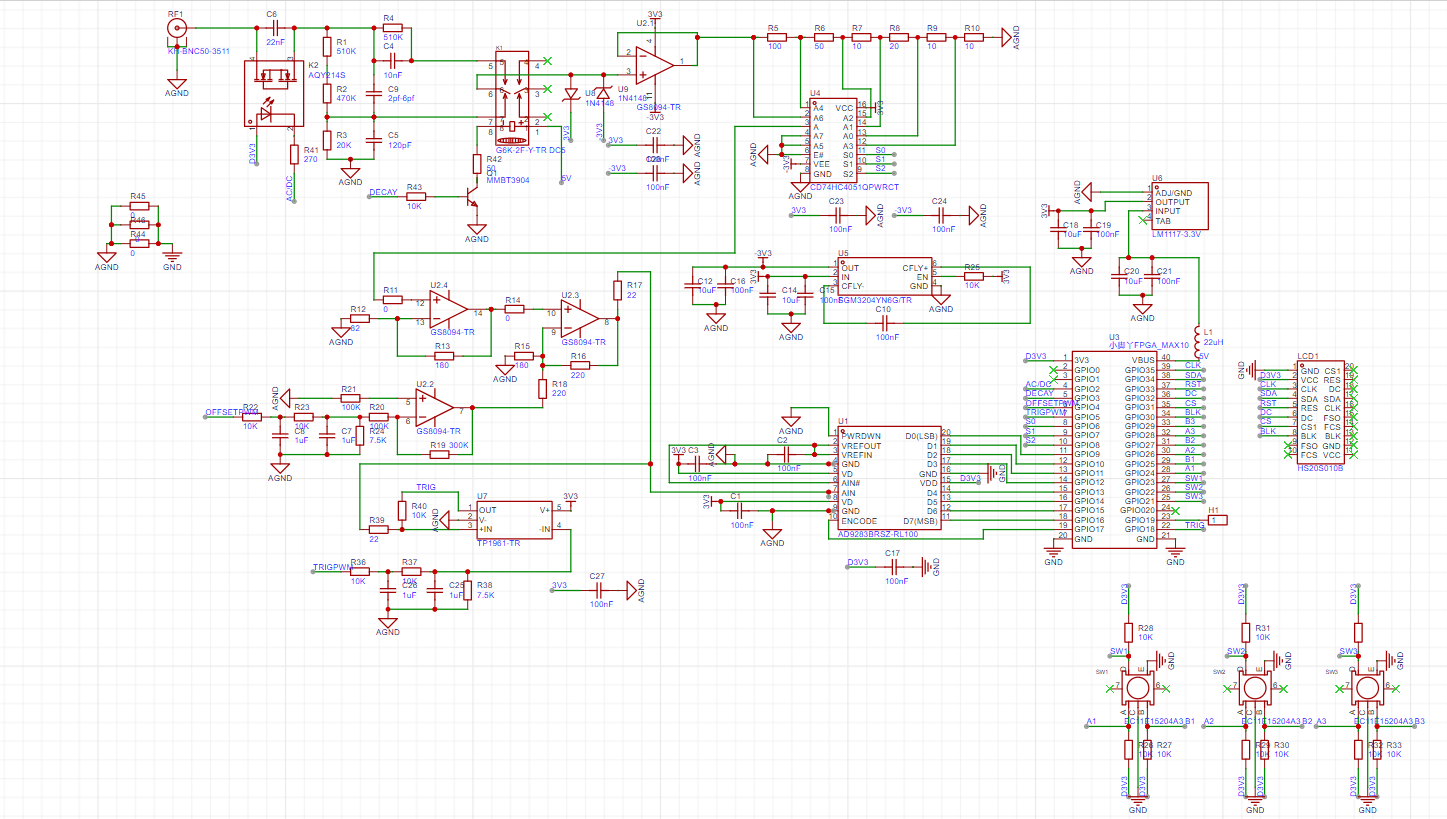

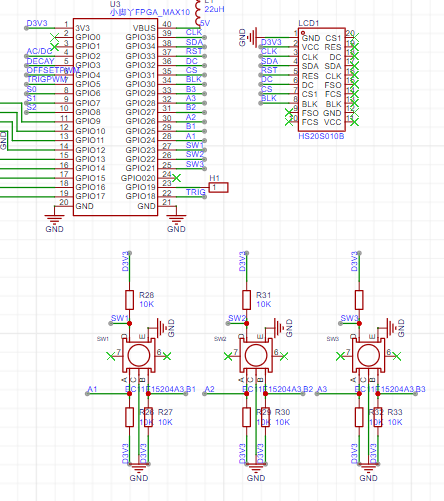

如上图是整体电路图,电路包含:输入衰减、输入跟随、增益选择、信号放大、信号偏移、高速ADC、FPGA部分、LCD显示屏和编码器部分。下面将逐步讲解各部分设计原理。

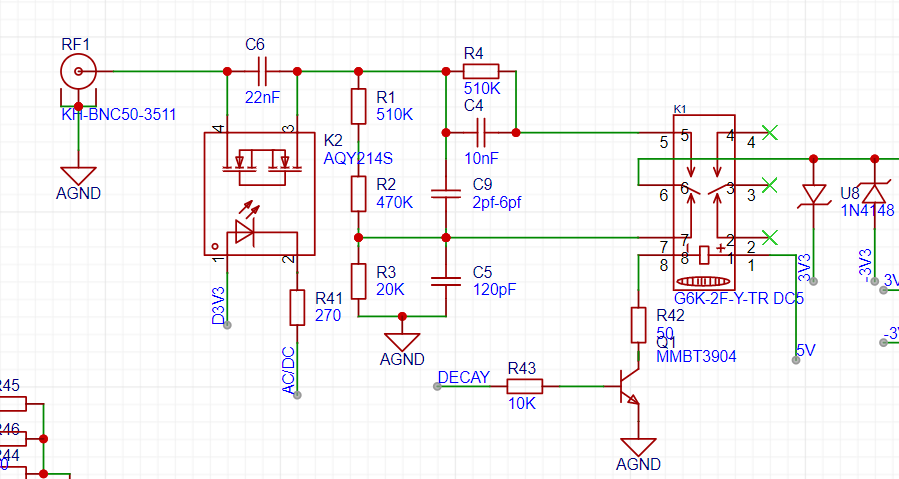

输入采用BNC插座,信号进入一个22nF小电容。该电容与后面的1M电阻网络可构成截止频率1/(2*pi*R*C)=7hz左右的高通滤波器。这样在交流耦合的时候可以滤除直流信号。采用一个光耦,当光耦导通时,可短路掉小电容,那么就时直流耦合,直流电可通过。后面电阻网络构成一个1倍或者1/50倍衰减,通过继电器可以选择是否需要衰减,从而实现较高电压的输入测量。衰减电阻网络需要搭配上电容来进行补偿。继电器后接两个肖特基二极管来限幅,保证运放和FPGA的安全。注意,信号继电器电磁铁有正负极,接反了无法吸合。

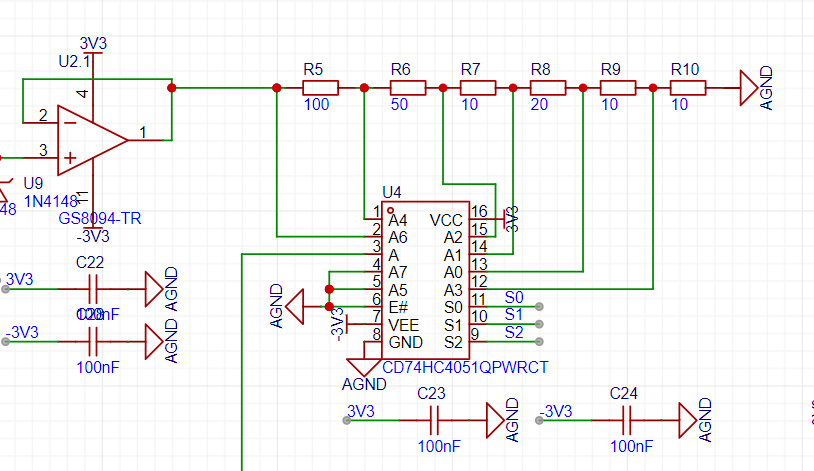

这一部分是信号衰减程控网络。外用电阻分压加模拟开关选通的形式,通过切换不同的接头来选择不同的挡位。所以电压挡位的切换实际是这部分加上前面继电器衰减的那部分共同完成的。这些阻值的选择,搭配起来正好可以实现1-2-5的挡位调节,最小10mV/div,最大10V/div。

这一部分是信号调理电路。U2.4运放构成一个1+(180/82)=3.2倍的同相比例放大电路。之后进入U2.3,该电路是一个加法器电路,同时具有1+(220/(180//220))=3.2倍的放大倍数。U2.2运放是将前面滤波电路形成的直流偏置电压进行4倍的放大。这几块电路将信号进行放大、偏移调理。

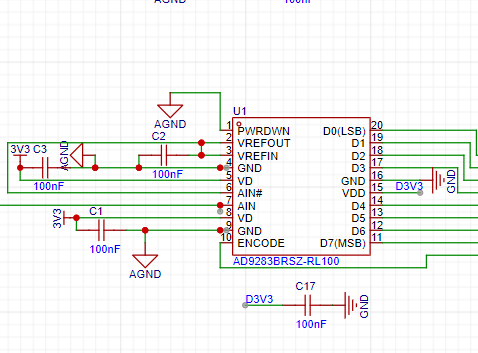

这个是100M高速的ADC电路。该芯片满量程1.024Vpp,差分输入0.512V,自带基准1.25v。所以将基准连到AIN#上,这样就变成了一个单端输入的ADC,输入电压为0.738~1.762V,正好与前级相适应。

这部分是FPGA和人机交互的部分,采用三个编码器,可以灵活调节各种参数。LCD采用240*320分辨率的屏幕,显示效果更好。

下面是功能介绍

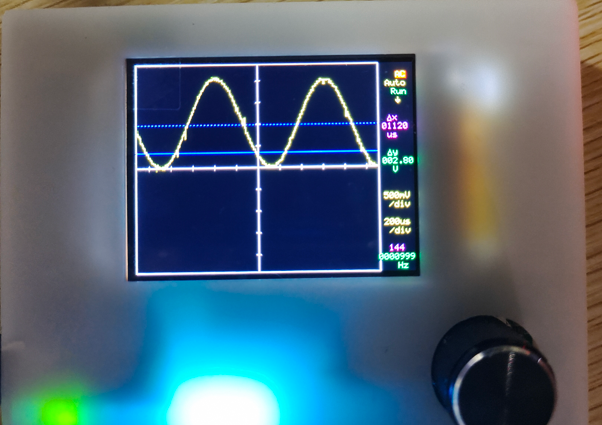

整体如上,有一个屏幕显示,三个编码器可以操作。最下面的编码器可以旋转来调节时基,按下后切换为触发电压调节。中间的编码器可以旋转调节垂直电压挡位,按下后切换为垂直偏移调节。上面的那个编码器是多功能,其余所有的功能都有它来实现。

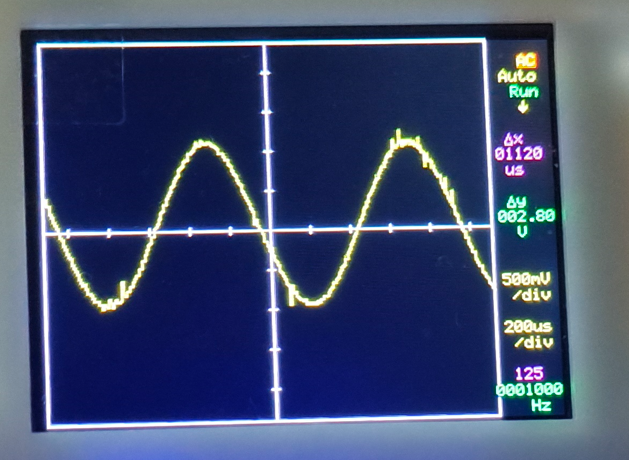

界面如图。有做一个预触发的设计,保证出发点在中心线上。右侧是各个功能,通过旋转上编码器选择功能项,按下可以改变对应功能项。第一行是AC/DC耦合选择。第二行是触发模式,有自动触发、标准触发、单次触发可以选择。第三行是暂停/运行的选择和显示。第四行是上升沿触发/下降沿触发的选择。下面两个是标尺测量,旋转到该选项,屏幕会出现标尺,通过旋转中编码器和下编码器来调节标尺实现测量。再往下两个挡位的显示。最下面绿色的是频率计,采用Verilog实现,通过表述一个数字的滞回比较器形成脉冲,然后去测量这个脉冲在一秒钟的次数计算得到。

如上图,虚线是代表0v的电平位置,而实线代表触发电平的位置。

如上图是测量标尺。

下面是硬件电路板的展示。

设计图

未生成预览图,请在编辑器重新保存一次

未生成预览图,请在编辑器重新保存一次BOM

暂无BOM

暂无BOM 克隆工程

克隆工程工程成员

知识产权声明&复刻说明

本项目为开源硬件项目,其相关的知识产权归创作者所有。创作者在本平台上传该硬件项目仅供平台用户用于学习交流及研究,不包括任何商业性使用,请勿用于商业售卖或其他盈利性的用途;如您认为本项目涉嫌侵犯了您的相关权益,请点击上方“侵权投诉”按钮,我们将按照嘉立创《侵权投诉与申诉规则》进行处理。

请在进行项目复刻时自行验证电路的可行性,并自行辨别该项目是否对您适用。您对复刻项目的任何后果负责,无论何种情况,本平台将不对您在复刻项目时,遇到的任何因开源项目电路设计问题所导致的直接、间接等损害负责。

评论