【更新中】这是一个8bit CPU!WLN08_03

简介

这是一个由74芯片打造的8bit CPU!32Byte ROM,8Byte RAM,8条指令,经典五级流水线,哈佛架构,可调主频,入门级8bit CPU,适合想了解CPU构造及运行原理的diyer。

简介:这是一个由74芯片打造的8bit CPU!32Byte ROM,8Byte RAM,8条指令,经典五级流水线,哈佛架构,可调主频,入门级8bit CPU,适合想了解CPU构造及运行原理的diyer。开源协议

:GPL 3.0

描述

这是一个由74芯片打造的8bit CPU!名为WLN08_03,硬件资源有32Byte ROM,8Byte RAM,8条指令,经典五级流水线,哈佛架构,可调主频,入门级8bit CPU,适合想了解CPU构造及运行原理的diyer。

工程更新中,各个模块正在测试,未最终定型,请勿打板(如果想自己研究也可自行魔改),敬请期待,点个关注等更新吧!

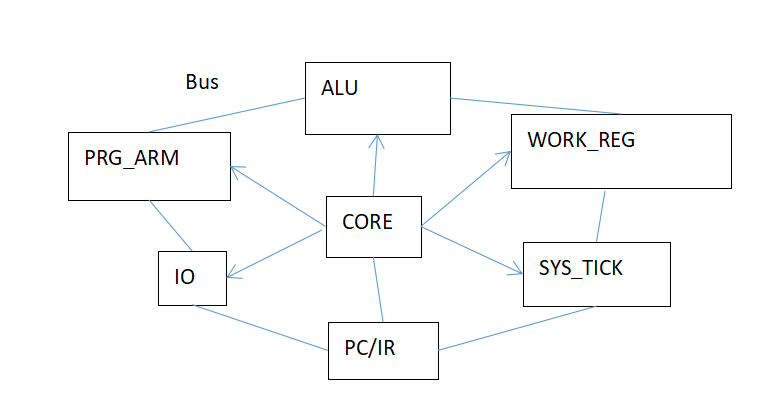

先大致讲一下该CPU的结构:大概有8个单独的模块,通过databus总线连接,core核单独控制各个模块,

sys_tick:系统时钟发生模块

alu:计算模块

work_reg:工作寄存器

prog_rom:程序存储器

pc/ir:程序计数器,指令寄存器等

core:CPU主核心,控制各个模块的逻辑

其它模块待补充。。。

工作原理待补充。。。

WLN08_03是WLN08_01的指令集精简版,为了更好的用独立74芯片复现出来而做的部分删减,早期WLN08_01能做到判断并跳转(相当于if),_03并没有这么高级的功能,只能执行顺序语句,没有分支跳转和alu比较。

WLN08_01框架图:

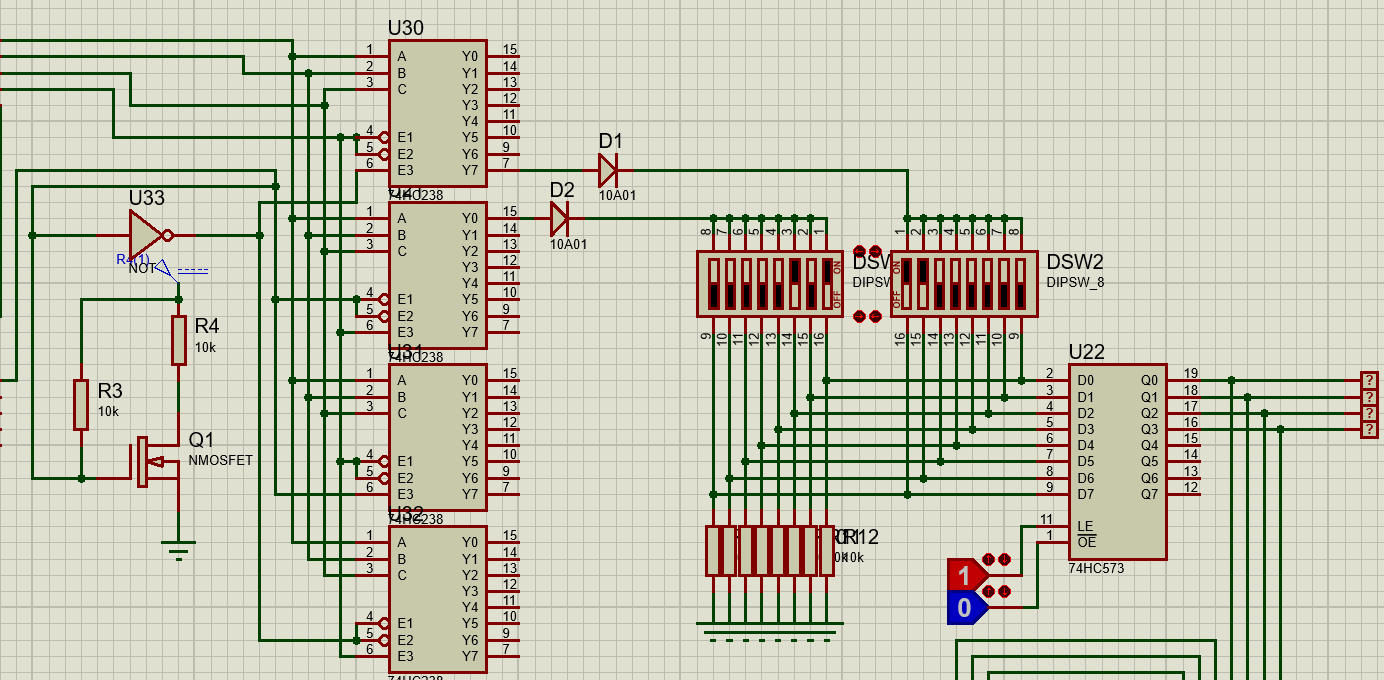

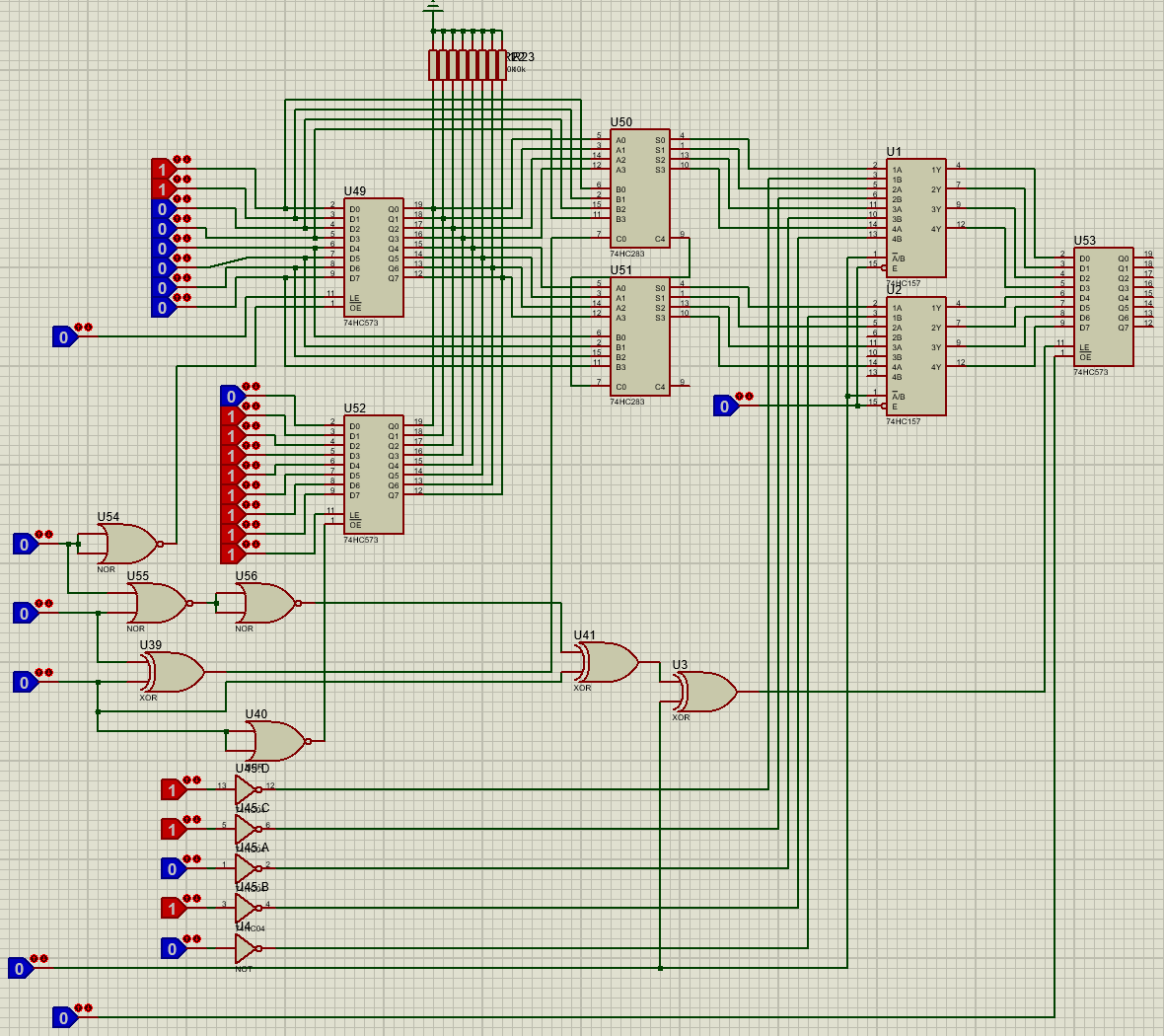

PROG_RAM

输入:addr[3:0] 地址选择 en:输出使能 databus[7:0]数据输出

功能:存储程序数据,只读

原理:使用8位拨码开关存储一字节,为了保持往上拨为1,往下拨为0的习惯,设计电路为选通该字节地址时输出要为高电平,但138为输出低电平有效,故选择238,拨码开关上方连接译码器输出,下方全部连接在一起并10K拉低连到数据输出缓冲器。地址选择部分由4片3-8译码器构成5-32译码器,数据输出缓冲器选择573,LE常为1,OE低电平输出有效。

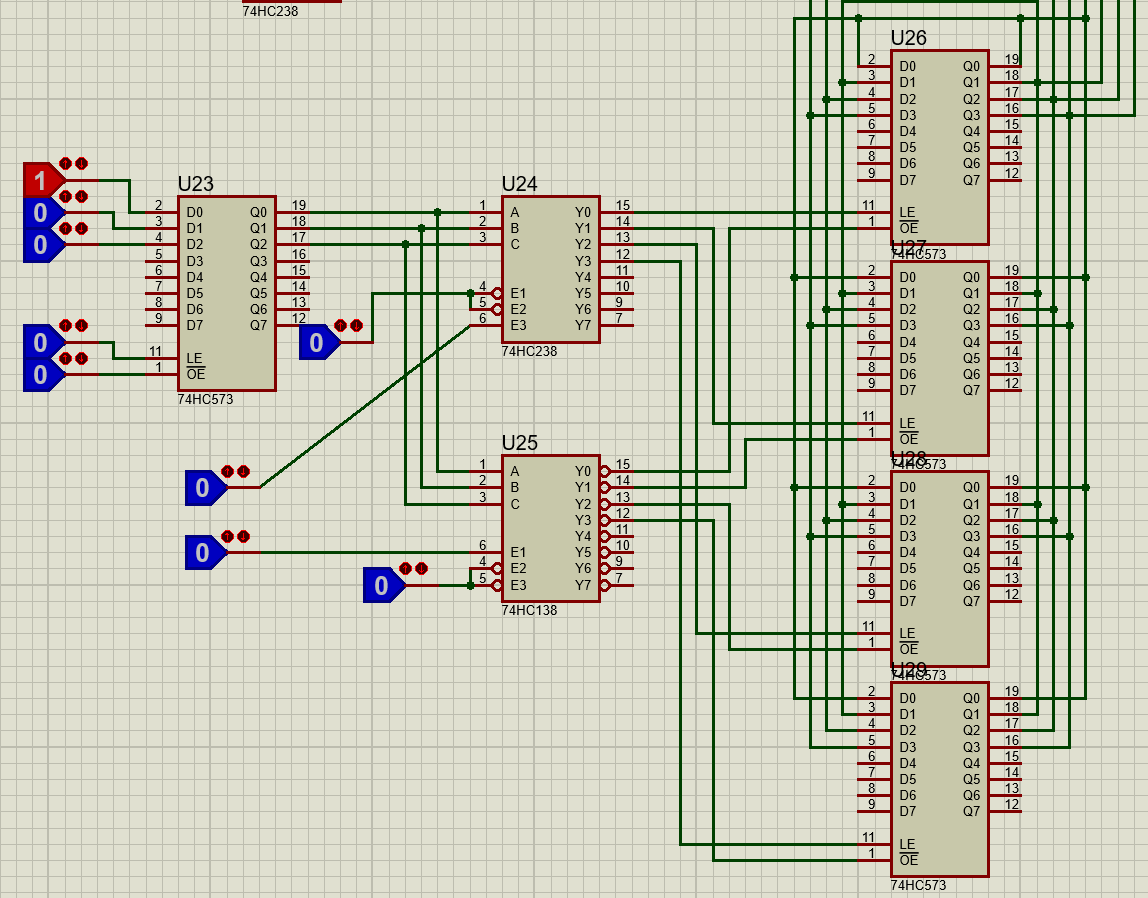

work_reg

输入:addr[2:0]地址选择 cp:上升沿地址锁存 en:低电平输出使能 read:上升沿读数据 write:上升沿写数据 databus[7:0]:数据总线

原理:工作寄存器由8个573构成这8个573输出输出全接到总线上,读写部分实现:先使用一个寄存器锁存地址,由于573的LE是高电平锁存数据,OE是低电平输出使能,即可使用138控制OE,238控制LE,并分别使用译码器的输出使能来控制读写。由于这8个573的输入和输出是接在总线上的,所以138和238必须保证同一时刻只能有一片在工作。

读reg时序:addr地址提供>cp上升沿锁存地址数据>释放databus>read使能

写reg时序:addr地址提供>cp上升沿锁存地址数据>databus准备数据>write使能

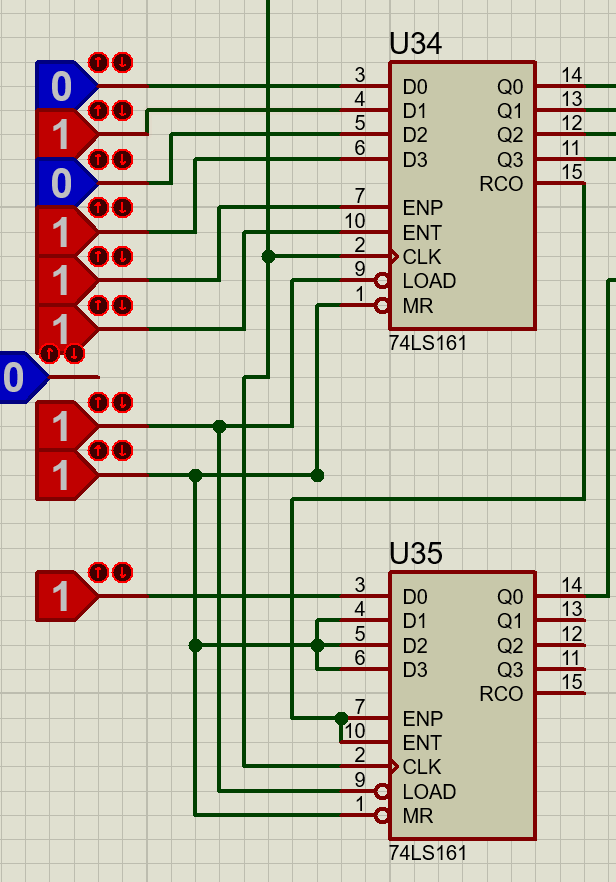

PC:这个没啥好说的,两个161组成32进制计数器,并且有预置数功能可相应jmp跳转指令,输出提供给程序存储器PROG_RAM。

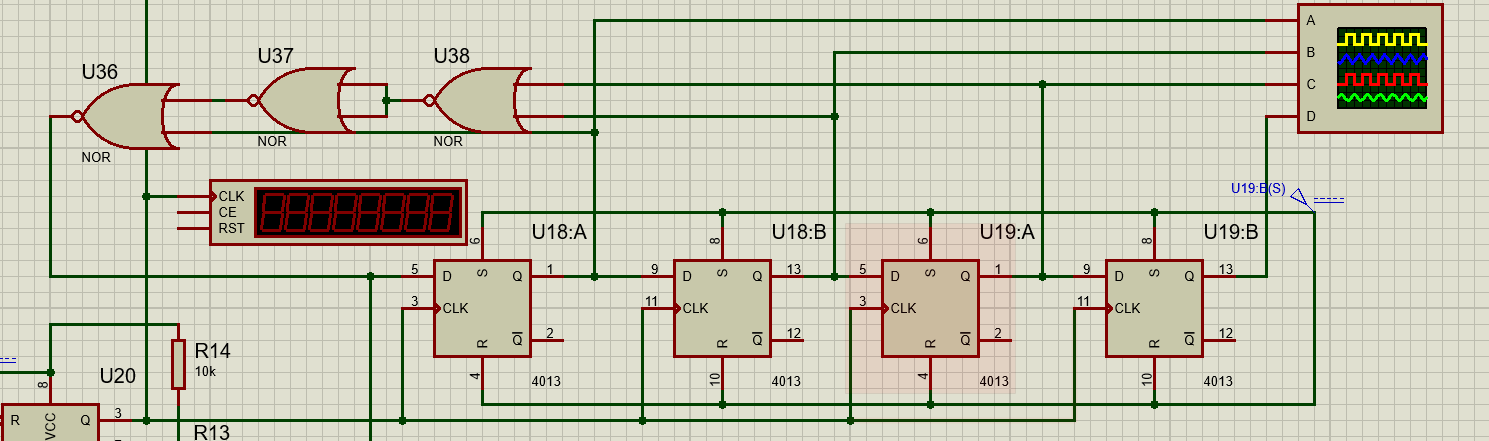

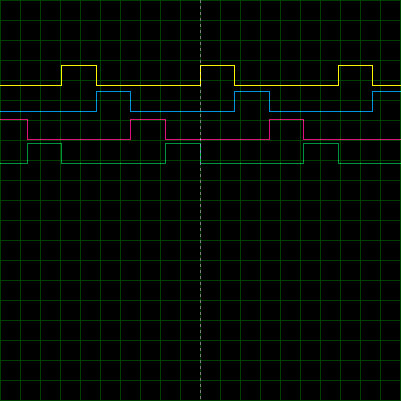

sys_tick:系统时钟模块,时钟源有555和MCU两种选择方式,频率范围1hz-10Khz,把时钟源输出的频率分频为4个顺序的step时钟,

T0-T3波形图如图:

ALU:计算模块共有四个运算模式:加,自加一,自减一,取反。原理自行理解,之后会说明。

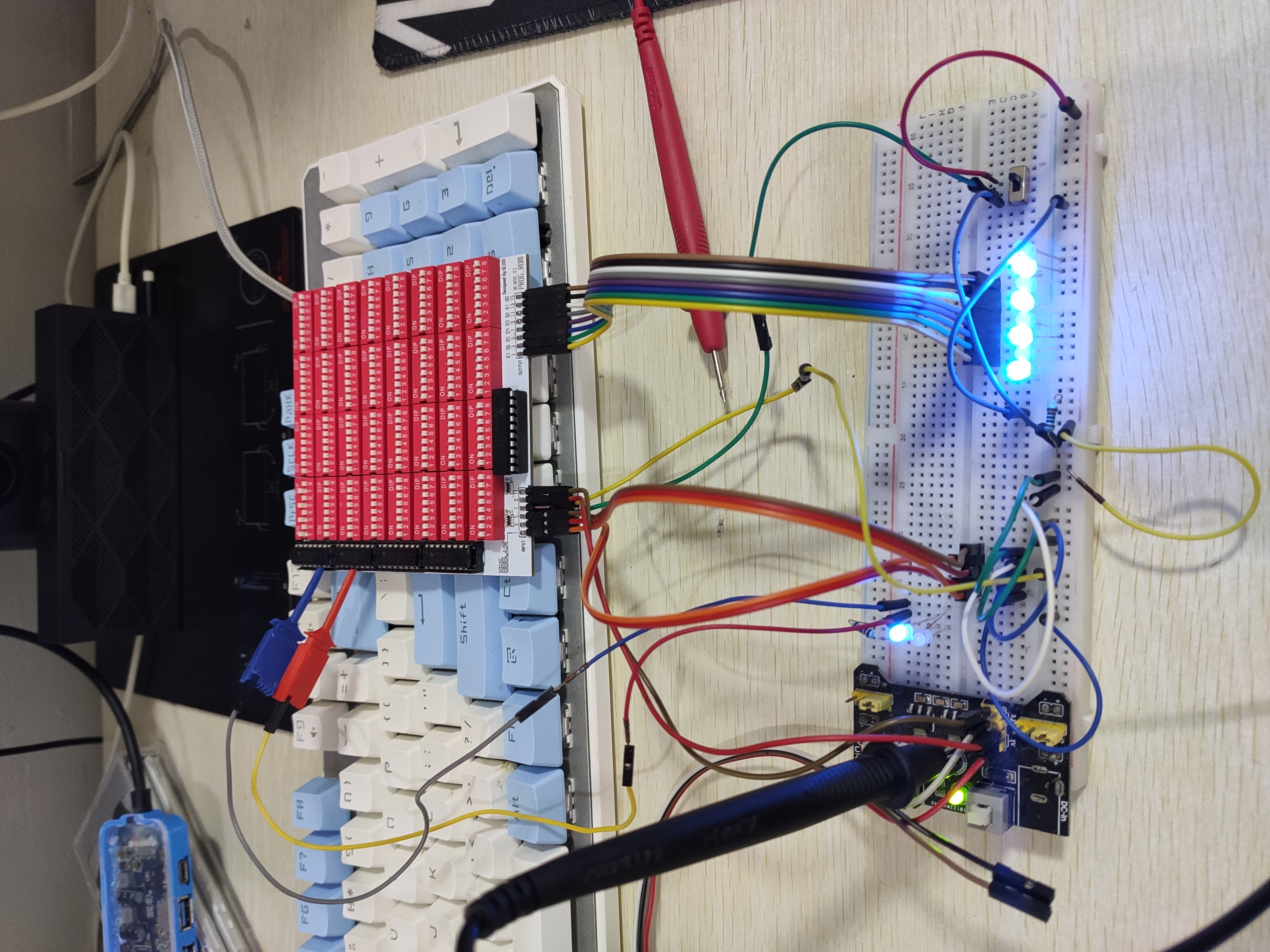

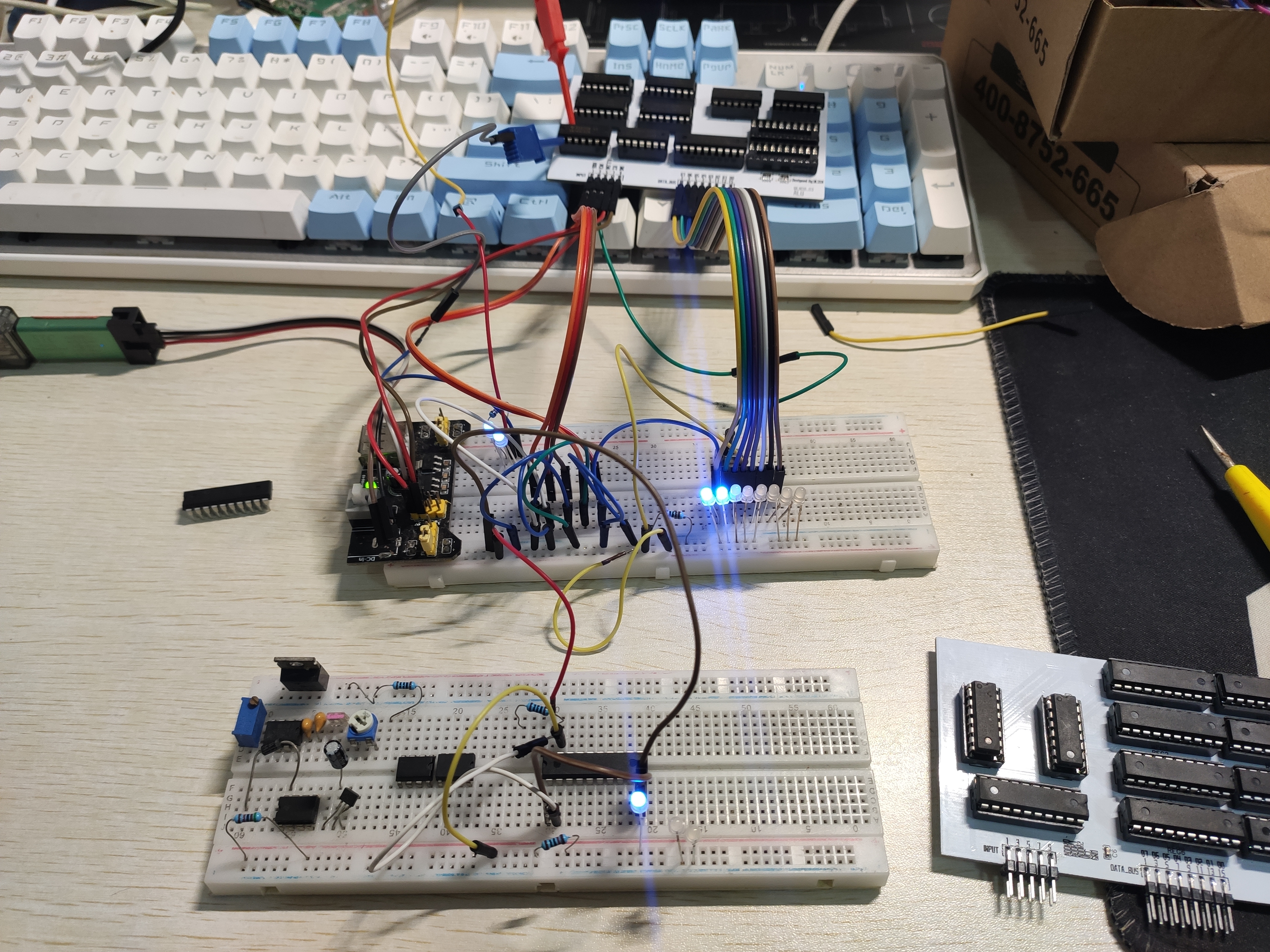

目前进度:测试SYS_TICK系统时钟最高速度和波形情况--OK;测试PC计数逻辑时序--OK;验证ALU功能--OK;测试work_reg功能--OK;验证prog_ram--OK。

各个模块验证OK,正在设计core模块。

说出来你们可能不信,在某宝买到了假芯片了,573发热,02引脚反了,导致进度拖延。。。

没错,就是在优信买的,在这里排雷了,买元器件还是去立创商城买正品吧(lcsc打钱!)。

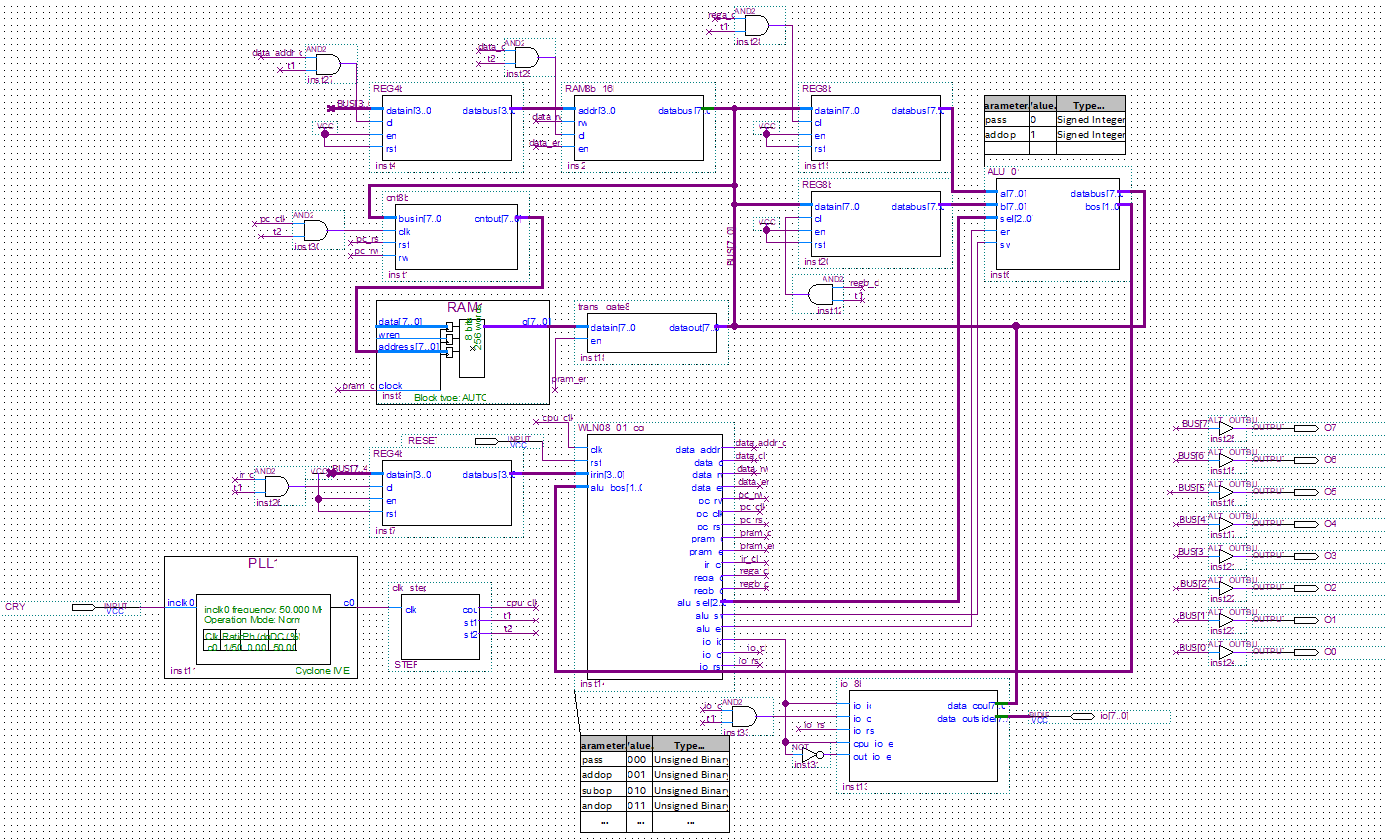

CORE设计:

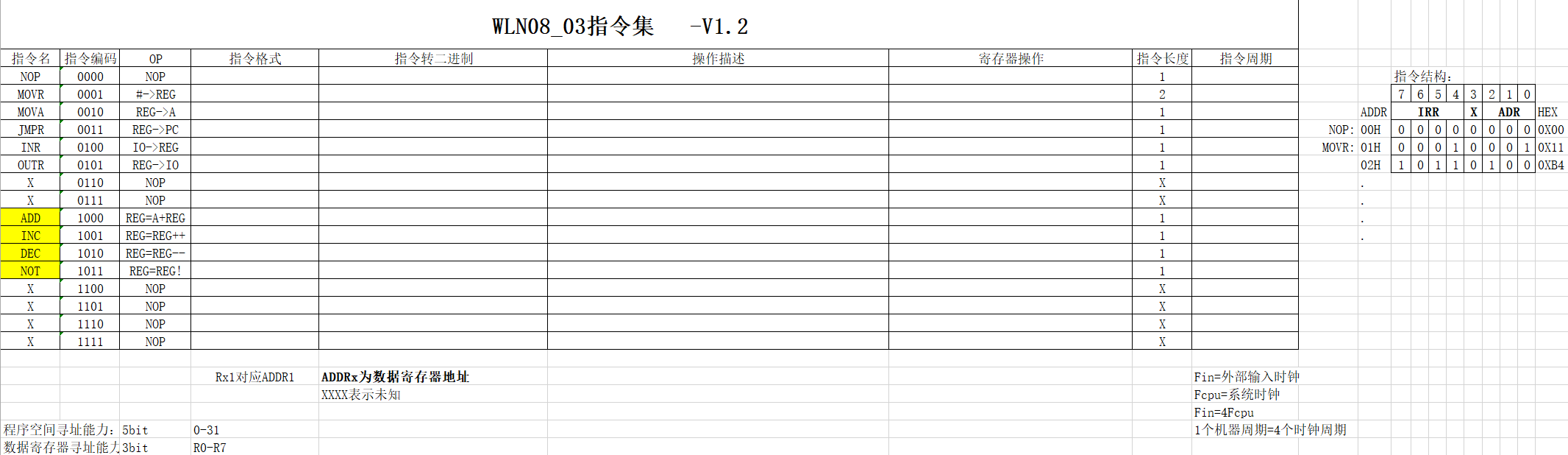

指令集:目前设计10条指令如下,正在写Verilog,之后设计电路实现。

测试功能中:

慢慢更新。。。。。。

设计图

未生成预览图,请在编辑器重新保存一次

未生成预览图,请在编辑器重新保存一次BOM

暂无BOM

暂无BOM 克隆工程

克隆工程工程成员

知识产权声明&复刻说明

本项目为开源硬件项目,其相关的知识产权归创作者所有。创作者在本平台上传该硬件项目仅供平台用户用于学习交流及研究,不包括任何商业性使用,请勿用于商业售卖或其他盈利性的用途;如您认为本项目涉嫌侵犯了您的相关权益,请点击上方“侵权投诉”按钮,我们将按照嘉立创《侵权投诉与申诉规则》进行处理。

请在进行项目复刻时自行验证电路的可行性,并自行辨别该项目是否对您适用。您对复刻项目的任何后果负责,无论何种情况,本平台将不对您在复刻项目时,遇到的任何因开源项目电路设计问题所导致的直接、间接等损害负责。

评论