专业版

artix7_core_board核心板

226

0

0

2

简介

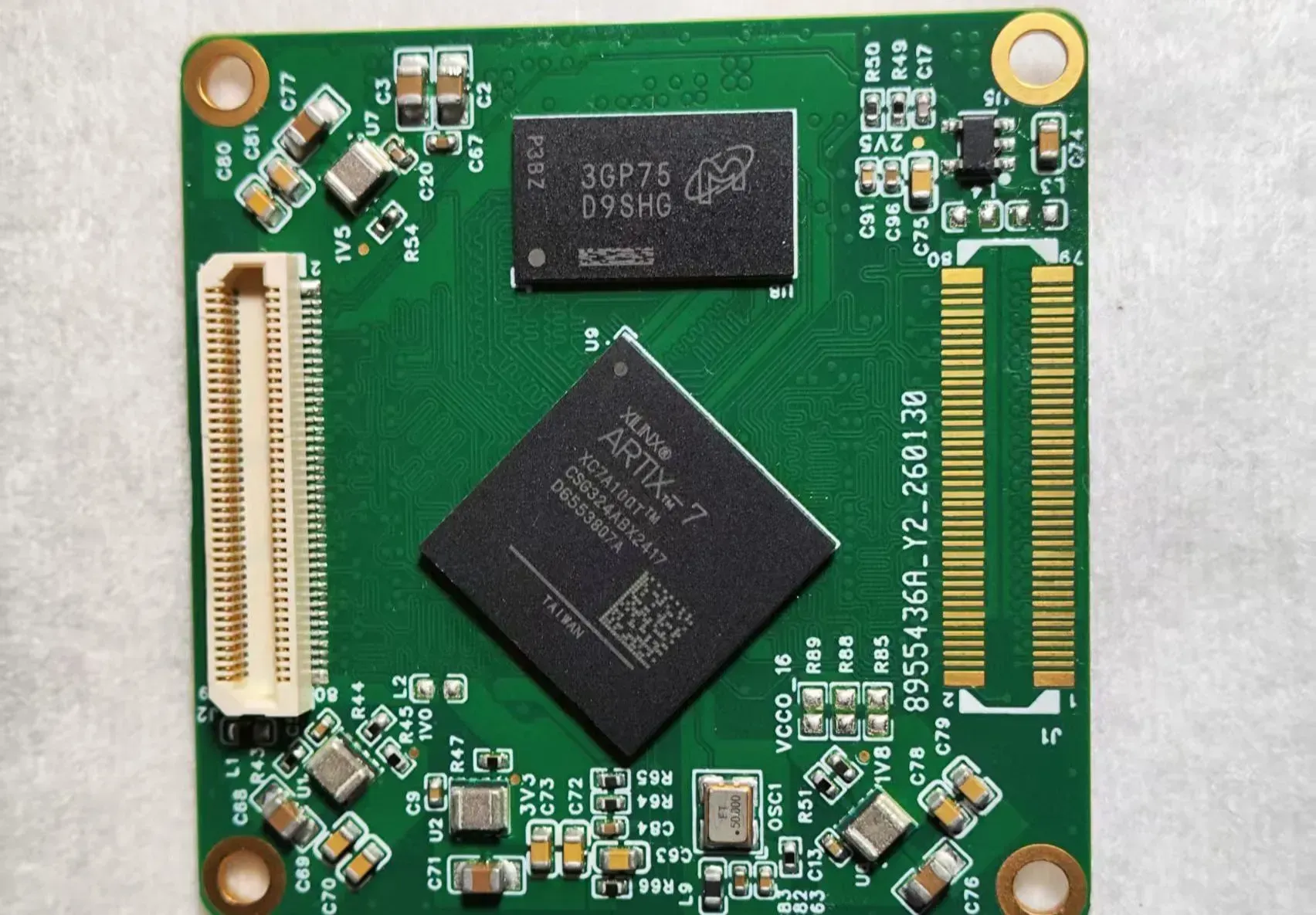

本工程基于XC7A100T-2CSG324I芯片,板载2Gbit镁光DDR3,通过板对板与背板连接器AXK5S80347YG引出大量IO的FPGA核心板。

简介:本工程基于XC7A100T-2CSG324I芯片,板载2Gbit镁光DDR3,通过板对板与背板连接器AXK5S80347YG引出大量IO的FPGA核心板。开源协议

:CC BY 3.0

创建时间:2026-03-12 21:59:04更新时间:2026-03-17 16:44:19

描述

项目简介

本项目基于Artix-7系列芯片,采用嘉立创6层盘中孔沉金的工艺,引出100个IO(48对差分),差分走线做了等长,引出IO对应Bank供电可选1.8V、2.5V和3.3V。供大家制作各种底板,实现多种功能。

原理解析(硬件说明)

主控为XC7A100T-2CSG324I,DDR3位宽16bit,可采样用镁光MT41K128M16TW-107 AIT:J TR,板对板与背板连接器采用AXK5S80347YG和AXK6S80447YG。

测试说明

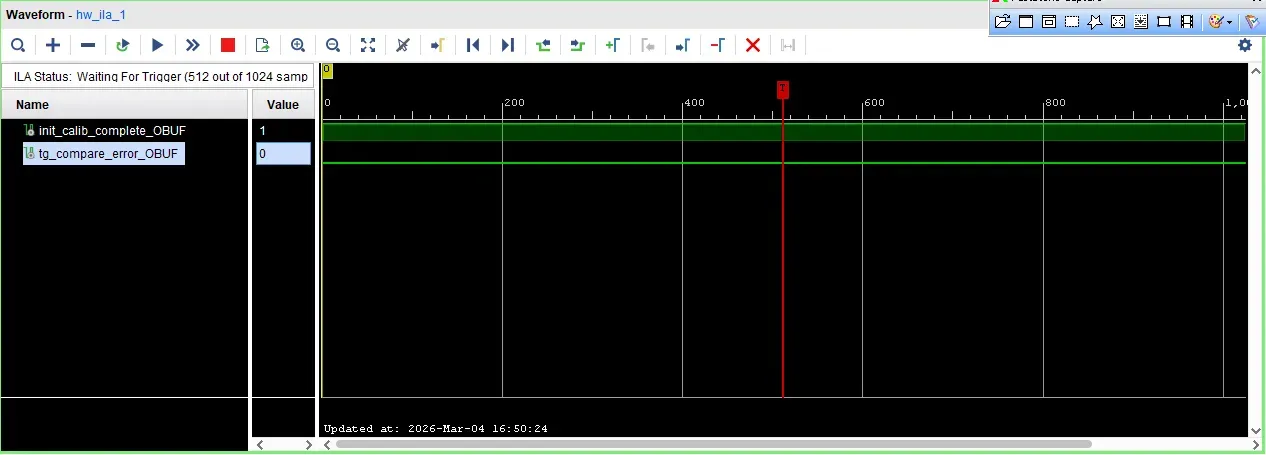

电源正常,下载程序正常,DDR3测试300MHz通过。

设计图

未生成预览图,请在编辑器重新保存一次

未生成预览图,请在编辑器重新保存一次BOM

暂无BOM

暂无BOM 克隆工程

克隆工程添加到专辑

0

0

分享

侵权投诉

工程成员

知识产权声明&复刻说明

本项目为开源硬件项目,其相关的知识产权归创作者所有。创作者在本平台上传该硬件项目仅供平台用户用于学习交流及研究,不包括任何商业性使用,请勿用于商业售卖或其他盈利性的用途;如您认为本项目涉嫌侵犯了您的相关权益,请点击上方“侵权投诉”按钮,我们将按照嘉立创《侵权投诉与申诉规则》进行处理。

请在进行项目复刻时自行验证电路的可行性,并自行辨别该项目是否对您适用。您对复刻项目的任何后果负责,无论何种情况,本平台将不对您在复刻项目时,遇到的任何因开源项目电路设计问题所导致的直接、间接等损害负责。

评论