AD9288双通道8位高速ADC 40/80/100MSPS

简介

AD9288双通道8位高速ADC 40/80/100MSPS

简介:AD9288双通道8位高速ADC 40/80/100MSPS开源协议

:LGPL 3.0

描述

AD9288是一款双核8位单芯片采样模数转换器(ADC),内置片内采样保持电路,专门针对低成本、低功耗、小尺寸和易用性进行了优化。该产品采用100 MSPS转换速率工作,在整个工作范围内都具有出色的动态性能。每个通道均可以独立工作。

该ADC只需一个3 V(2.7 V至3.6 V)单电源和一个编码时钟就能充分发挥工作性能。对于大多数应用来说,无需外部基准电压源或驱动器件。数字输出为TTL/CMOS兼容,单独的输出电源引脚支持3.3 V或2.5 V逻辑接口。

编码输入为TTL/CMOS兼容,8位数字输出可以采用+3 V(2.5 V至3.6 V)电源供电。用户可选项提供各种省电模式、数字数据格式和数字数据定时方案组合。在省电模式下,数字输出被置为高阻状态。

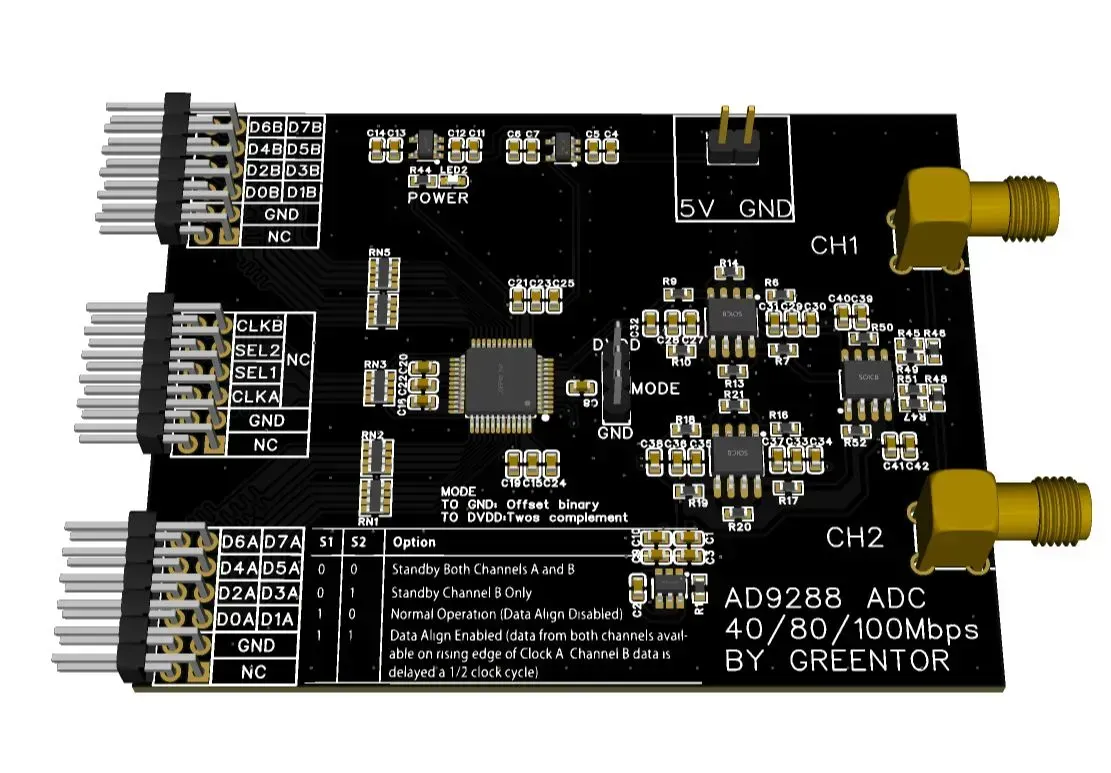

硬件电路

该adc模块的设计方案为常见的高速并口ADC的电路布置,包括电源、前端放大调理、ADC外围、数字输出。

前端信号调理使用LMH6643MAX作跟随器,实现衰减,然后通过AD8138ARZ差分放大电路作为ADC信号差分输入驱动。数字信号输出采用三个PMOD口,S1,S2引脚可以配置ADC两个通道的使能与时序

驱动程序

①采用FPGA

|

`timescale 1ns / 1ps

module AD9288(

input sys_clk,

input sys_rst_n,

input [7:0] AD9288_DIN_A,

input [7:0] AD9288_DIN_B,

output reg AD9288_CLK_A,

output reg AD9288_CLK_B,

output reg [7:0] AD9288_DOUT_A,

output reg [7:0] AD9288_DOUT_B,

output S1,S2

);

parameter CLK_A_DIV = 2;

parameter CLK_B_DIV = 2;

reg [15:0] clka_div_cnt;

reg [15:0] clkb_div_cnt;

assign S1 = 1, S2 = 1;

always @(posedge sys_clk) begin

if (!sys_rst_n) begin

AD9288_DOUT_A<=0;

end

else begin

AD9288_DOUT_A <= AD9288_DIN_A;

end

end

always @(posedge sys_clk) begin

if (!sys_rst_n) begin

clka_div_cnt <= 0;

AD9288_CLK_A <= 0;

end

else begin

if(clka_div_cnt == CLK_A_DIV - 1)begin

clka_div_cnt <= 0;

AD9288_CLK_A <= ~AD9288_CLK_A;

end

else begin

clka_div_cnt <= clka_div_cnt + 1'b1;

AD9288_CLK_A <= AD9288_CLK_A;

end

end

end

always @(posedge sys_clk) begin

if (!sys_rst_n) begin

AD9288_DOUT_B<=0;

end

else begin

AD9288_DOUT_B <= AD9288_DIN_B;

end

end

always @(posedge sys_clk) begin

if (!sys_rst_n) begin

clkb_div_cnt <= 0;

AD9288_CLK_B <= 0;

end

else begin

if(clkb_div_cnt == CLK_A_DIV - 1)begin

clkb_div_cnt <= 0;

AD9288_CLK_B <= ~AD9288_CLK_B;

end

else begin

clkb_div_cnt <= clkb_div_cnt + 1'b1;

AD9288_CLK_B <= AD9288_CLK_B;

end

end

end

endmodule

|

已验证,正常使用

②采用STM32等单片机

TODO

测试验证

注意事项

1.该ADC芯片有直接国产替代如MXT2088等

2.AD9288芯片价格不高,性能优良,很适合以低成本做一个高性能的ADC模块,测试采购的芯片价格在10多元。购买运放注意水深。

设计图

未生成预览图,请在编辑器重新保存一次

未生成预览图,请在编辑器重新保存一次BOM

暂无BOM

暂无BOM 克隆工程

克隆工程工程成员

知识产权声明&复刻说明

本项目为开源硬件项目,其相关的知识产权归创作者所有。创作者在本平台上传该硬件项目仅供平台用户用于学习交流及研究,不包括任何商业性使用,请勿用于商业售卖或其他盈利性的用途;如您认为本项目涉嫌侵犯了您的相关权益,请点击上方“侵权投诉”按钮,我们将按照嘉立创《侵权投诉与申诉规则》进行处理。

请在进行项目复刻时自行验证电路的可行性,并自行辨别该项目是否对您适用。您对复刻项目的任何后果负责,无论何种情况,本平台将不对您在复刻项目时,遇到的任何因开源项目电路设计问题所导致的直接、间接等损害负责。

评论