USB转I2S、DSD异步时钟声卡

简介

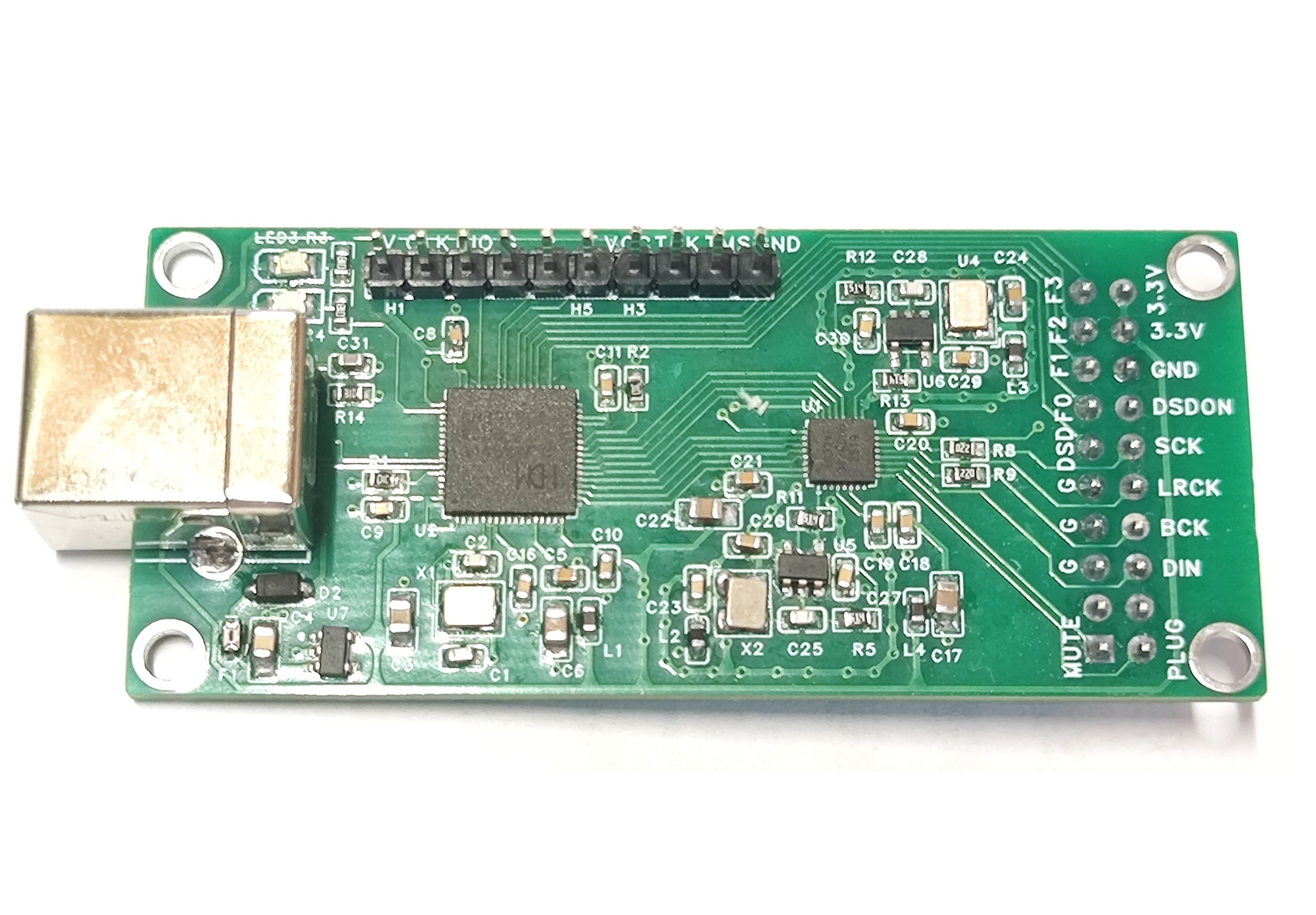

国产方案USB转I2S、DSD方案,代替Amanero以及XMOS方案。接口完全兼容Amanero方案,

简介:国产方案USB转I2S、DSD方案,代替Amanero以及XMOS方案。接口完全兼容Amanero方案,开源协议

:GPL 3.0

描述

USB转I2S、DSD,采用异步接口,单片机负责USB高速数据处理,FPGA负责接口协议发送。接口完全兼容Amanero方案,

USB采用UAC2.0实现,无需驱动支持windows、linux、ios。可以支持到主机最大1%的频偏(每96帧掉1帧)。

支持44.1kHz、48kHz、88.2kHz、96kHz、176.4kHz、192kHz、352.8kHz、384kHz、705.6kHz、768kHz的32位、24位、16位、DSD64、DSD128、DSD256、DSD512编码格式。

注意:DSD的驱动是有特殊协议的,在Amanero方案中采用VID和PID的识别方式,本方案的DSD实现借用了Amanero的VID和PID,如果要自定义需要修改linux内核驱动文件并重新编译。

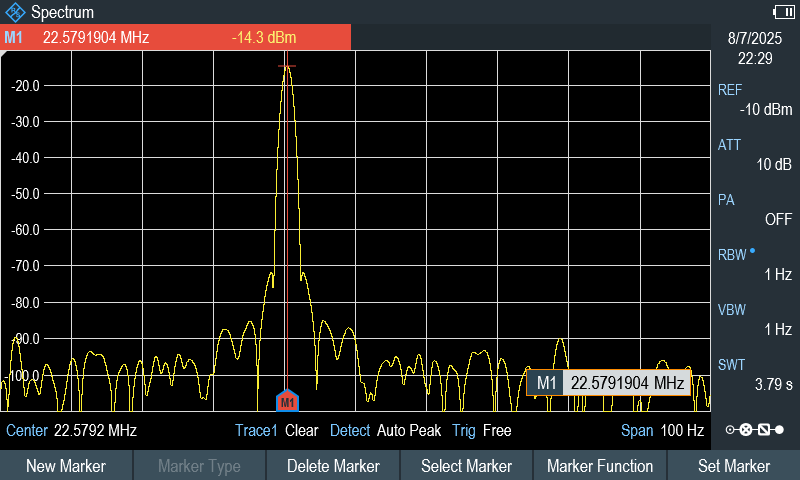

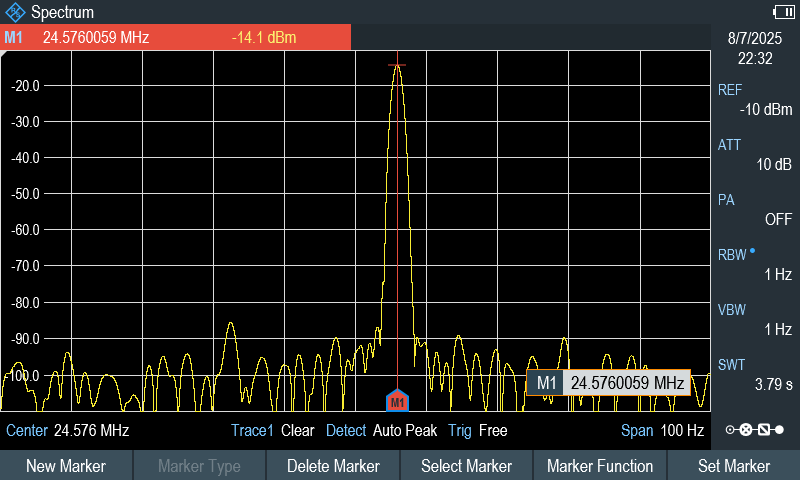

系统采用了两片温补晶振+削峰正弦波转CMOS电平的电路,24.576MHz晶振采用DSB321SDN,22.5792MHz晶振采用DSB3215CL,若采用其他晶振非削峰正弦波电平的请自行修改电路,使用0ohm电阻旁路削峰正弦波转CMOS电平的电路。这两个晶振焊过几次,频率稳定性如下:(罗德FPH,仪器本身声称频率稳定性为0.5PPM)

本工程在https://oshwhub.com/lovelonelytime/usbtoi2s的基础上修改而来。

在FPGA时钟中SDC约束不是很完整,并且有时序违例,基本不用管。

注意需要把PLL输入改一下映射,在quartus中完成综合后,需要修改simulation\modelsim\usb2i2s.vo的文件,将.inclk({vcc,vcc,vcc,\clk_24576~input_o }),改成.inclk({vcc,vcc,vcc,\mck_o~0_combout }),

编译请参考芯片官方文档教程,已经做好的文件在cpld\usb2i2s_batch.bin和mcu\CH32V307WCU6\obj\CH32V307WCU6.hex下直接烧录既可。

设计图

未生成预览图,请在编辑器重新保存一次

未生成预览图,请在编辑器重新保存一次BOM

暂无BOM

暂无BOM 克隆工程

克隆工程知识产权声明&复刻说明

本项目为开源硬件项目,其相关的知识产权归创作者所有。创作者在本平台上传该硬件项目仅供平台用户用于学习交流及研究,不包括任何商业性使用,请勿用于商业售卖或其他盈利性的用途;如您认为本项目涉嫌侵犯了您的相关权益,请点击上方“侵权投诉”按钮,我们将按照嘉立创《侵权投诉与申诉规则》进行处理。

请在进行项目复刻时自行验证电路的可行性,并自行辨别该项目是否对您适用。您对复刻项目的任何后果负责,无论何种情况,本平台将不对您在复刻项目时,遇到的任何因开源项目电路设计问题所导致的直接、间接等损害负责。

评论