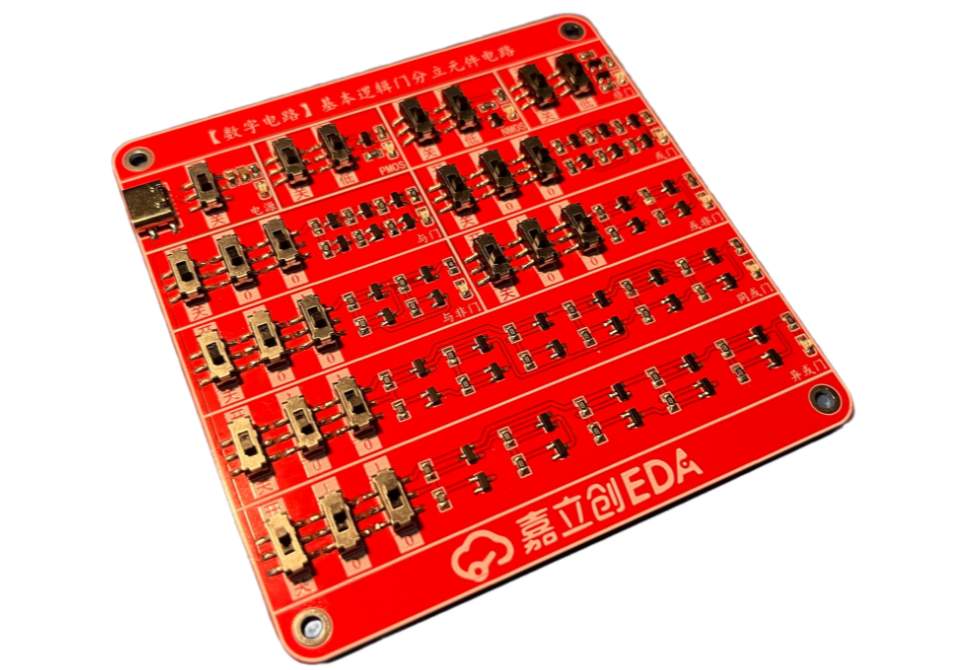

【数字电路】基本逻辑门分立元件电路

简介

逻辑门是数字电路上的基本单元,能够实现各种逻辑关系。基本逻辑门分立元件电路采用MOS管搭建而成,实现验证与、或、非、与非、或非、同或和异或等逻辑运算。

简介:逻辑门是数字电路上的基本单元,能够实现各种逻辑关系。基本逻辑门分立元件电路采用MOS管搭建而成,实现验证与、或、非、与非、或非、同或和异或等逻辑运算。开源协议

:GPL 3.0

描述

一、项目简介

逻辑门是数字电路上的基本单元,能够实现各种逻辑关系。基本逻辑门分立元件电路采用MOS管搭建而成,实现验证与、或、非、与非、或非、同或和异或等逻辑运算。

二、原理解析

1.1 PMOS

PMOS是指N型衬底(SUB)、P沟道,靠空穴的流动运送电流的MOS管。形成导通沟道需要负电荷吸引,低电平导通,高电平截止。

图1-1-1 PMOS符号与结构示意图

使用PMOS控制时通常作为上管,放置在负载上方,常在PMOS上加一个上拉电阻,使PMOS栅极保持一个稳定的高电平初始状态,防止PMOS栅极电平受到外界干扰产生不确定状态,保证PMOS默认在关闭状态。当P0给低电平时,PMOS打开导通,LED亮起;当P0给高电平时,PMOS关闭截止,LED熄灭。

图1-1-2 PMOS开关控制电路图

1.2 NMOS

NMOS是指P型衬底(SUB)、N沟道,靠电子的流动运送电流的MOS管。形成导通沟道需要正电荷吸引,高电平导通,低电平截止。

图1-2-1 NMOS符号与结构示意图

使用NMOS控制时通常作为下管,放置在负载下方,常在NMOS上加一个下拉电阻,使NMOS栅极保持一个稳定的低电平初始状态,防止NMOS栅极电平受到外界干扰产生不确定状态,保证NMOS默认在关闭状态。当N0给低电平时,NMOS关闭截止,LED熄灭;当N0给高电平时,NMOS打开导通,LED亮起。

图1-2-2 NMOS开关控制电路图

1.3 CMOS

CMOS由PMOS与NMOS以对称互补的形式组成,C表示“互补”。静态功耗低,开关速度快,抗干扰能力强,工作效率高,集成度高,性能优越。

2.1 与门

与门(AND gate),又称逻辑积电路。 只有当输入都为高电平(逻辑1)时,输出才为高电平(逻辑1),否则输出为低电平(逻辑0)。

图2-1-1 与门逻辑符号(矩形国标符号与形状特征符号)

表1-1 与门真值表

|

输入 |

输出 |

|

|

A1 |

B1 |

Y1 |

|

0 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

1 |

逻辑表达式:Y1=A1·B1

图2-1-2 CMOS与门电路

工作原理为:

① 当A1输入低电平,B1输入低电平时,Q1,Q2,Q5导通,Q3,Q4,Q6截止,Y1输出低电平;

② 当A1输入低电平,B1输入高电平时,Q2,Q5,Q6导通,Q1,Q3,Q4截止,Y1输出低电平;

③ 当A1输入高电平,B1输入低电平时,Q1,Q4,Q5导通,Q2,Q3,Q6截止,Y1输出低电平;

④ 当A1输入高电平,B1输入高电平时,Q3,Q4,Q6导通,Q1,Q2,Q5截止,Y1输出高电平;

图2-1-3 CMOS与门电路工作原理图图

2.2 或门

或门(OR gate),又称逻辑和电路。只要输入中有一个为高电平(逻辑1)时,输出就为高电平(逻辑1);只有当输入都为低电平(逻辑0)时,输出才为低电平(逻辑0)。

图2-2-1 或门逻辑符号(矩形国标符号与形状特征符号)

表1-2 或门真值表

|

输入 |

输出 |

|

|

A2 |

B2 |

Y2 |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

1 |

逻辑表达式:Y2=A2+B2

图2-2-2 CMOS或门电路

工作原理为:

① 当A2输入低电平,B2输入低电平时,Q1,Q2,Q6导通,Q3,Q4,Q5截止,Y2输出低电平;

② 当A2输入低电平,B2输入高电平时,Q1,Q3,Q5导通,Q2,Q4,Q6截止,Y2输出高电平;

③ 当A2输入高电平,B2输入低电平时,Q2,Q3,Q4导通,Q1,Q5,Q6截止,Y2输出高电平;

④ 当A2输入高电平,B2输入高电平时,Q3,Q4,Q5导通,Q1,Q2,Q6截止,Y2输出高电平;

图2-2-3 CMOS或门工作原理图

2.3 非门

非门(NOT gate),又称逻辑否电路。当输入为低电平(逻辑0)时,输出为高电平(逻辑1);当输入为高电平(逻辑1)时,输出为低电平(逻辑0)。

图2-3-1 非门逻辑符号(矩形国标符号与形状特征符号)

表1-3 非门真值表

|

输入 |

输出 |

|

A3 |

Y3 |

|

0 |

1 |

|

1 |

0 |

逻辑表达式:Y3=A3’

图2-3-2 CMOS非门电路

工作原理为:

① 当A3输入低电平时,Q1导通,Q2截止,Y3输出高电平;

② 当A3输入高电平时,Q2导通,Q1截止,Y3输出低电平;

图2-3-3 CMOS非门电路工作原理图

2.4 与非门

与非门(NAND gate)是与门和非门的叠加结合。只有当输入都为高电平(逻辑1)时,输出为低电平(逻辑0),否则输出为高电平(逻辑1)。

图2-4-1 与非门逻辑符号(矩形国标符号与形状特征符号)

表1-4 与非门真值表

|

输入 |

输出 |

|

|

A4 |

B4 |

Y4 |

|

0 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

逻辑表达式:Y4=(A4·B4)’

图2-4-2 CMOS与非门

工作原理为:

① 当A4输入低电平,B4输入低电平时,Q1,Q2导通,Q3,Q4截止,Y4输出高电平;

② 当A4输入低电平,B4输入高电平时,Q2,Q4导通,Q1,Q3截止,Y4输出高电平;

③ 当A4输入高电平,B4输入低电平时,Q1,Q3导通,Q2,Q4截止,Y4输出高电平;

④ 当A4输入高电平,B4输入高电平时,Q3,Q4导通,Q1,Q2截止,Y4输出低电平;

图2-4-3 CMOS与非门工作原理图

2.5 或非门

或非门(NOR gate)是或门和非门的叠加结合。只有当输入都为低电平(逻辑0)时,输出为高电平(逻辑1),否则输出为低电平(逻辑0)。

图2-5-1 或非门逻辑符号(矩形国标符号与形状特征符号)

表1-5 或非门真值表

|

输入 |

输出 |

|

|

A5 |

B5 |

Y5 |

|

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

0 |

逻辑表达式:Y5=(A5+B5)’

图2-5-2 CMOS或非门电路

工作原理为:

① 当A5输入低电平,B5输入低电平时,Q1,Q2导通,Q3,Q4截止,Y5输出高电平;

② 当A5输入低电平,B5输入高电平时,Q1,Q4导通,Q2,Q3截止,Y5输出低电平;

③ 当A5输入高电平,B5输入低电平时,Q2,Q3导通,Q1,Q4截止,Y5输出低电平;

④ 当A5输入高电平,B5输入高电平时,Q3,Q4导通,Q1,Q2截止,Y5输出低电平;

图2-5-3 CMOS或非门电路工作原理图

2.6 同或门

同或门(XNOR gate)可以只用与非门或者或非门组成,输入相同,输出为高电平(逻辑1),输入相异,输出为低电平(逻辑0)。

图2-6-1 同或门逻辑符号(矩形国标符号与形状特征符号)

图2-6-2 同或门实现图

表1-6 同或门真值表

|

输入 |

输出 |

|

|

A6 |

B6 |

Y6 |

|

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

1 |

逻辑表达式:Y6=A6⊙B6=A6·B6 + A6’·B6’

图2-6-3 CMOS同或门电路

工作原理为:

①当A6输入低电平,B6输入低电平时,Q1,Q2,Q3,Q4,Q6,Q9导通,Q5,Q7,Q8,Q10,Q11,Q12截止,Y6输出高电平;

②当A6输入低电平,B6输入高电平时,Q3,Q4,Q5,Q7,Q10,Q12导通,Q1,Q2,Q6,Q8,Q9,Q11截止,Y6输出低电平;

③当A6输入高电平,B6输入低电平时,Q1,Q2,Q5,Q8,Q10,Q11导通,Q3,Q4,Q6,Q7,Q9,Q12截止,Y6输出低电平;

④当A6输入高电平,B6输入高电平时,Q5,Q6,Q7,Q8,Q11,Q12导通,Q1,Q2,Q3,Q4,Q9,Q10截止,Y6输出高电平;

图2-6-4 CMOS同或门电路工作原理图

2.7 异或门

异或门(XOR gate)由一个与门,或门和与非门组成,输入相异,输出为高电平(逻辑1),输入相同,输出为低电平(逻辑0)。

图2-7-1 异或门逻辑符号(矩形国标符号与形状特征符号)

图2-7-2 异或门实现图

表1-7 异或门真值表

|

输入 |

输出 |

|

|

A7 |

B7 |

Y7 |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

逻辑表达式:Y7=A7⊕B7=A7·B7’ + A7’·B7

图2-7-3 CMOS异或门电路

工作原理为:

① 当A7输入低电平,B7输入低电平时,Q1,Q2,Q3,Q4,Q8导通,Q5,Q6,Q7,Q9,Q10截止,Y7输出低电平;

② 当A7输入低电平,B7输入高电平时,Q3,Q4,Q5,Q6,Q10导通,Q1,Q2,Q7,Q8,Q9截止,Y7输出高电平;

③ 当A7输入高电平,B7输入低电平时,Q1,Q2,Q5,Q7,Q9导通,Q3,Q4,Q6,Q8,Q10截止,Y7输出高电平;

④ 当A7输入高电平,B7输入高电平时,Q5,Q6,Q7,Q9,Q10导通,Q1,Q2,Q3,Q4,Q8截止,Y7输出低电平;

图2-7-4 CMOS异或门电路工作原理图

三、项目设计

1.原理图设计

首先,打开嘉立创EDA,创建新工程并命名为【数字电路】基本逻辑门分立元件电路,将原理图文件命名为:SCH_基本逻辑门分立元件电路。

其次,进行器件选型,这里所有元器件都选用贴片器件,元器件都可以在嘉立创EDA的元件库中进行搜索,每一个元器件在立创商城中都有唯一的商品编号,电源接口选用6Pin的TYPE-C母座,使用LED来显示验证各逻辑门的运算关系。

最后,绘制电路原理图,各逻辑门按模块电路划分进行绘制,注明各个电路的作用,添加各逻辑门的符号,真值表和表达式,便于理解学习。

图3-1-1 SCH_电源输入电路

图3-1-2 SCH_PMOS和NMOS电路

图3-1-3 SCH_与门电路

图3-1-4 SCH_或门电路

图3-1-5 SCH_非门电路

图3-1-6 SCH_与非门电路

图3-1-7 SCH_或非门电路

图3-1-8 SCH_同或门电路

图3-1-9 SCH_异或门电路

2.物料清单

|

BOM_基本逻辑门分立元件电路 |

||||||

|

序号 |

名称 |

参数 |

位号 |

数量 |

封装 |

商品编号 |

|

1 |

电阻 |

10K |

R2,R5~R11,R13~R18,R20,R21,R23~R26,R28~R31, R33~R44,R46~R55 |

46 |

R0805 |

C17414 |

|

1K |

R1,R3,R4,R12,R19, R22,R27,R32,R45,R56 |

10 |

C17513 |

|||

|

2 |

电容 |

10uF |

C1 |

1 |

C0805 |

C40894 |

|

100nF |

C2 |

1 |

C38141 |

|||

|

3 |

PMOS |

FSS2301M A1SHB |

Q1,Q3~Q5,Q9~Q11, Q15,Q17,Q18,Q21,Q22, Q25~Q30,Q37~Q41 |

23 |

SOT23 |

C2926139 |

|

4 |

NMOS |

FSS2302S A2SHB |

Q2,Q6~Q8,Q12~Q14, Q16,Q19,Q20,Q23,Q24, Q31~Q36,Q42~Q46 |

23 |

SOT23 |

C2926140 |

|

5 |

开关 |

SS-3235S-L3 |

SW1~SW25 |

25 |

SW-SMD_SS-3235S-L3.00 |

C381098 |

|

6 |

LED |

红灯 |

LED1~LED10 |

10 |

LED0805 |

C84256 |

|

7 |

USB 连接器 |

TYPE-C |

USB1 |

1 |

USB-C-SMD_TYPE-C-31-M-29 |

C2689969 |

|

8 |

铜柱 |

M3 |

H1~H4 |

4 |

M3X10-6 |

C551322 |

3.PCB设计

在完成原理图设计后,经过检查电路与网络连接正确后点击顶部菜单栏的 “设计 ”→ “转换原理图到PCB”(快捷键为Alt+I),然后将PCB文件保存到工程文件中,并命名为:PCB_基本逻辑门分立元件电路。

在绘制边框设计时,控制在10cm*10cm之内,这里的边框为10cm*10cm,添加5mm的圆角,可以到嘉立创免费打样~

在进行器件布局时,所有器件放置于顶层,各逻辑门电路按模块划分摆放,可以通过顶部菜单栏中的“设计”→“交叉选择”(快捷键Shift+X)功能快速摆放元器件。在摆放相同元器件时尽量统一方向,方便焊接。

在进行布线时以底层走线为主,优先走直线,需要拐弯的地方以圆弧拐弯或钝角为主。完成走线检查DRC无误后,添加泪滴和覆铜。

最后,在板上添加丝印标注说明,使电路更加清晰明了。

图3-2-1 PCB布局布线参考图

顶面绘制完成后,在背面放置丝印标识各逻辑门的符号,真值表和表达式,清晰各个逻辑门的逻辑运算关系,方便理解学习。

图3-2-2 基本逻辑运算丝印赏析图

四、电路调试

1.器件焊接

第一,先焊接TYPE-C接口;第二,PMOS/NMOS;第三,LED,电阻和电容,最后焊接开关。注意焊接时PMOS和NMOS不要焊错,各逻辑门电路中,上方朝左的为PMOS,下方朝右的是NMOS;LED上面的电阻为1K,其余的均为10K;电容为滤波作用,可以不焊接。

图4-1-1 PCB装配图

在进行焊接时,可在嘉立创EDA的工具栏中点击焊接辅助工具,实时交互方便焊接。注意焊接过程中用电安全手不要接触到烙铁头,避免烫伤。

焊接时元器件对准位置,检查型号是否正确。焊接顺序应遵循从低到高原则进行,避免影响小器件的焊接。

焊接贴片元器件用镊子夹住时,要等焊锡凝固后再移走镊子,否则容易造成虚焊。焊接过程注意是否虚焊漏焊,避免影响电路性能,导致电路不能正常工作。

图4-1-2 PCB空板-顶面

图4-1-3 PCB空板-底面

图4-1-4 PCBA实物图

图4-1-5 3D渲染图

2.上电调试

若焊工比较粗糙,在焊接完一种元器件,可以目测检查是否短路,也可用万用表检查。焊接完成后需要使用万用表检查电源与地是否短路,焊接过程中有没有出现短路以及断路的情况,检查无误后方能进行上电测试。建议采用分步调试,避免其他电路的干扰。

2.1 电源电路

插入TYPE-C通上电后,拨动开关至上方开,电源状态指示灯亮起,电源给整个板子供电,各逻辑门有独立电源开关进行控制,各逻辑门验证时建议单独控制使用。

图4-2-1 电源开关电路

2.2 PMOS电路

拨动打开PMOS电源开关,PMOS电路正常工作。

- 当输入电平控制开关至低时,即PMOS输入低电平,指示灯亮起;

- 当输入电平控制开关至高时,即PMOS输入高电平,指示灯熄灭。

图4-2-2 PMOS验证工作图

2.3 NMOS电路

拨动打开NMOS电源开关,NMOS电路正常工作。

- 当输入电平控制开关至低时,即NMOS输入低电平,指示灯熄灭;

- 当输入电平控制开关至高时,即NMOS输入高电平,指示灯亮起。

图4-2-3 NMOS验证工作图

2.4 与门

拨动打开与门电源开关,与门电路正常工作。

- 当输入电平控制开关拨到00时,输出低电平,指示灯熄灭;

- 当输入电平控制开关拨到01时,输出低电平,指示灯熄灭;

- 当输入电平控制开关拨到10时,输出低电平,指示灯熄灭;

- 当输入电平控制开关拨到11时,输出高电平,指示灯亮起;

图4-2-4 与门验证工作图

2.5或门

拨动打开或门电源开关,或门电路正常工作。

- 当输入电平控制开关拨到00时,输出低电平,指示灯熄灭;

- 当输入电平控制开关拨到01时,输出高电平,指示灯亮起;

- 当输入电平控制开关拨到10时,输出高电平,指示灯亮起;

- 当输入电平控制开关拨到11时,输出高电平,指示灯亮起;

图4-2-5 或门验证工作图

2.6非门

拨动打开非门电源开关,非门电路正常工作。

- 当输入电平控制开关拨到0时,输出高电平,指示灯亮起;

- 当输入电平控制开关拨到1时,输出低电平,指示灯熄灭;

图4-2-6 非门验证工作图

2.7与非门

拨动打开与非门电源开关,与非门电路正常工作。

- 当输入电平控制开关拨到00时,输出高电平,指示灯亮起;

- 当输入电平控制开关拨到01时,输出高电平,指示灯亮起;

- 当输入电平控制开关拨到10时,输出高电平,指示灯亮起;

- 当输入电平控制开关拨到11时,输出低电平,指示灯熄灭;

图4-2-7 与非门验证工作图

2.8或非门

拨动打开或非门电源开关,或非门电路正常工作。

- 当输入电平控制开关拨到00时,输出高电平,指示灯亮起;

- 当输入电平控制开关拨到01时,输出低电平,指示灯熄灭;

- 当输入电平控制开关拨到10时,输出低电平,指示灯熄灭;

- 当输入电平控制开关拨到11时,输出低电平,指示灯熄灭;

图4-2-8 或非门验证工作图

2.9同或门

拨动打开同或门电源开关,同或门电路正常工作。

- 当输入电平控制开关拨到00时,输出高电平,指示灯亮起;

- 当输入电平控制开关拨到01时,输出低电平,指示灯熄灭;

- 当输入电平控制开关拨到10时,输出低电平,指示灯熄灭;

- 当输入电平控制开关拨到11时,输出高电平,指示灯亮起;

图4-2-9 同或门验证工作图

2.10异或门

拨动打开异或门电源开关,异或门电路正常工作。

- 当输入电平控制开关拨到00时,输出低电平,指示灯熄灭;

- 当输入电平控制开关拨到01时,输出高电平,指示灯亮起;

- 当输入电平控制开关拨到10时,输出高电平,指示灯亮起;

- 当输入电平控制开关拨到11时,输出低电平,指示灯熄灭;

图4-2-10 异或门验证工作图

设计图

未生成预览图,请在编辑器重新保存一次

未生成预览图,请在编辑器重新保存一次BOM

暂无BOM

暂无BOM 克隆工程

克隆工程知识产权声明&复刻说明

本项目为开源硬件项目,其相关的知识产权归创作者所有。创作者在本平台上传该硬件项目仅供平台用户用于学习交流及研究,不包括任何商业性使用,请勿用于商业售卖或其他盈利性的用途;如您认为本项目涉嫌侵犯了您的相关权益,请点击上方“侵权投诉”按钮,我们将按照嘉立创《侵权投诉与申诉规则》进行处理。

请在进行项目复刻时自行验证电路的可行性,并自行辨别该项目是否对您适用。您对复刻项目的任何后果负责,无论何种情况,本平台将不对您在复刻项目时,遇到的任何因开源项目电路设计问题所导致的直接、间接等损害负责。

评论