DCDC降压原理验证板

简介

用过几款DCDC降压芯片,原理知之甚少,按照芯片手册设计,似懂非懂,问题不断。于是产生搭一个DCDC降压芯片的想法,彻底搞懂原理。过程包括各个模块的仿真,原理图,PCB,测试等。

简介:用过几款DCDC降压芯片,原理知之甚少,按照芯片手册设计,似懂非懂,问题不断。于是产生搭一个DCDC降压芯片的想法,彻底搞懂原理。过程包括各个模块的仿真,原理图,PCB,测试等。开源协议

:GPL 3.0

描述

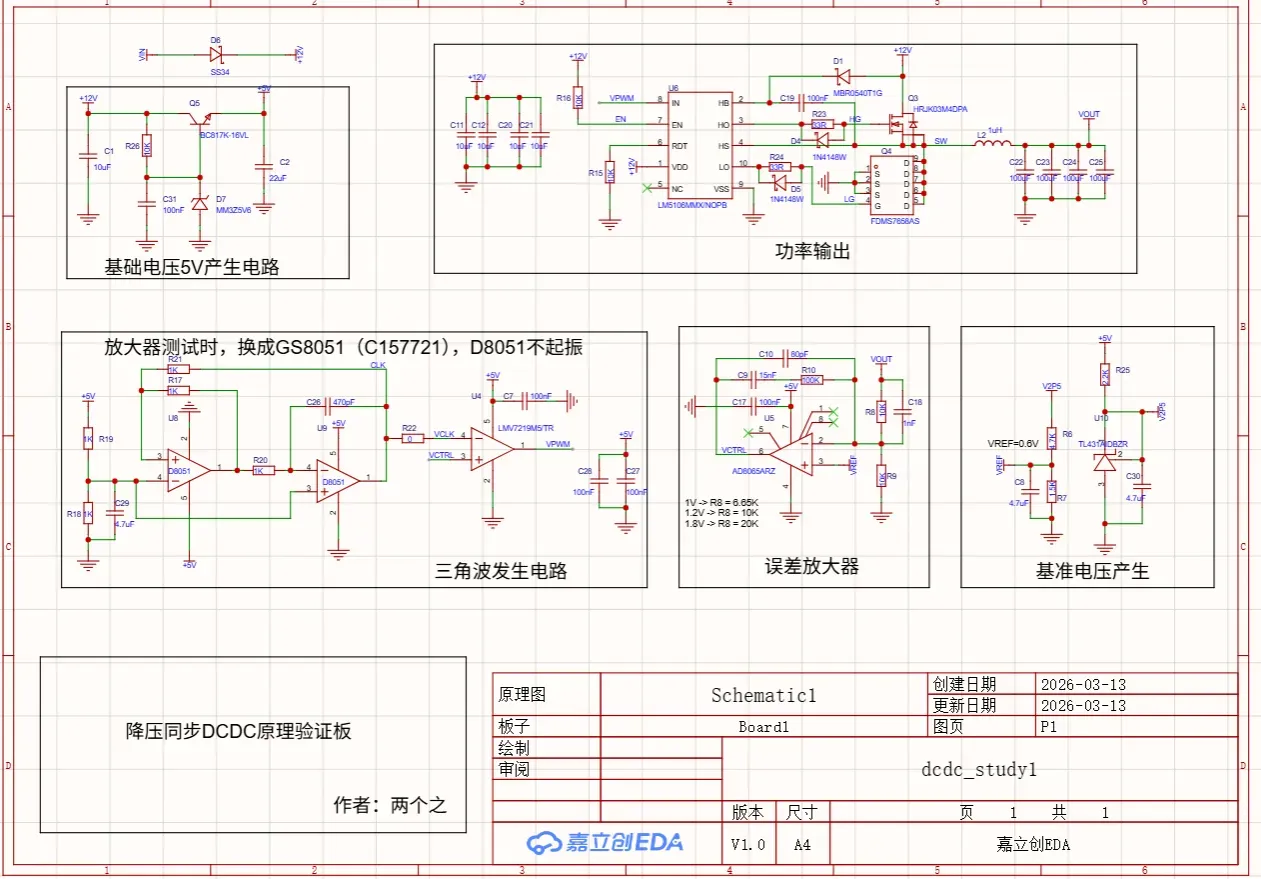

一,原理图

1.1 基础电压5V产生电路。使用NPN管BC817,和5.6V的稳压管,稳压管的5.6V减去NPN管的0.7V,约为5V。multisim仿真该电路,负载到100mA都不会有明显的压差,本电路实际负载少于30mA, 所以够用了。

1.2 基准电压产生电路。用低压给FPGA供电比较多,所以基准电压为0.6V,通过TLV431产生2.5V,然后分压得到0.6V。测试了1V,1.2V,1.8V, 达到效果。

1.3 三角波产生电路。此部分电路到第三版,换了四款放大器,到GS8051才能产生稳定的三角波,频率是420KHZ, 前面两版我用FPGA驱动DAC904来产生三角波,也可以使用。 波形有点消顶,并不影响使用。

1.4 误差放大器,网上有比较多原理说明,或者问一下豆包。开始调试的时候,反馈电容(C18)用的比较小,只有150pf,输出电压振荡,增交到1nf,电压稳定,纹波较小。

1.5 功率输出电路。使用半桥驱动芯片LM5106,该芯片驱动MOS管的时候,需要加个二极管,否则MOS管发热严重。两个MOS管是从华为电源模块PW22ARAB上拆的,没试过其它的。输出电容使用4个6.3V,100uf的陶瓷电容,实测在10A的负载电流情况下,纹波很小。

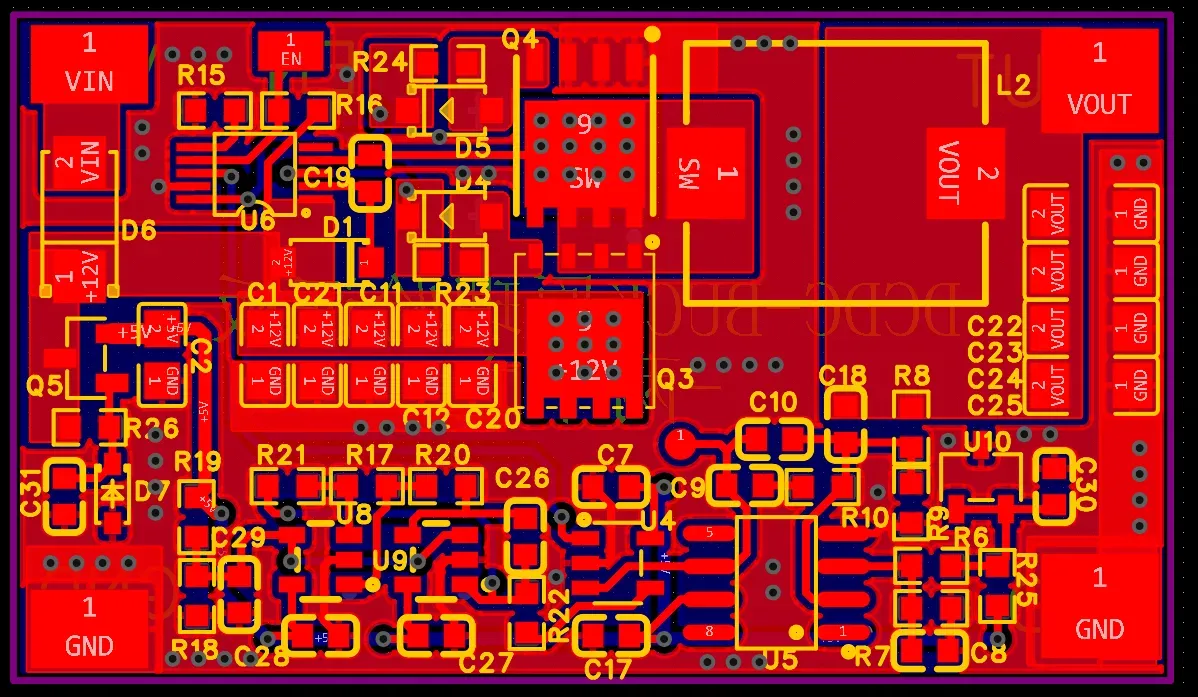

二,PCB效果

使用嘉立创两层板,四层板在信号干扰和散热上应该有更好的效果。

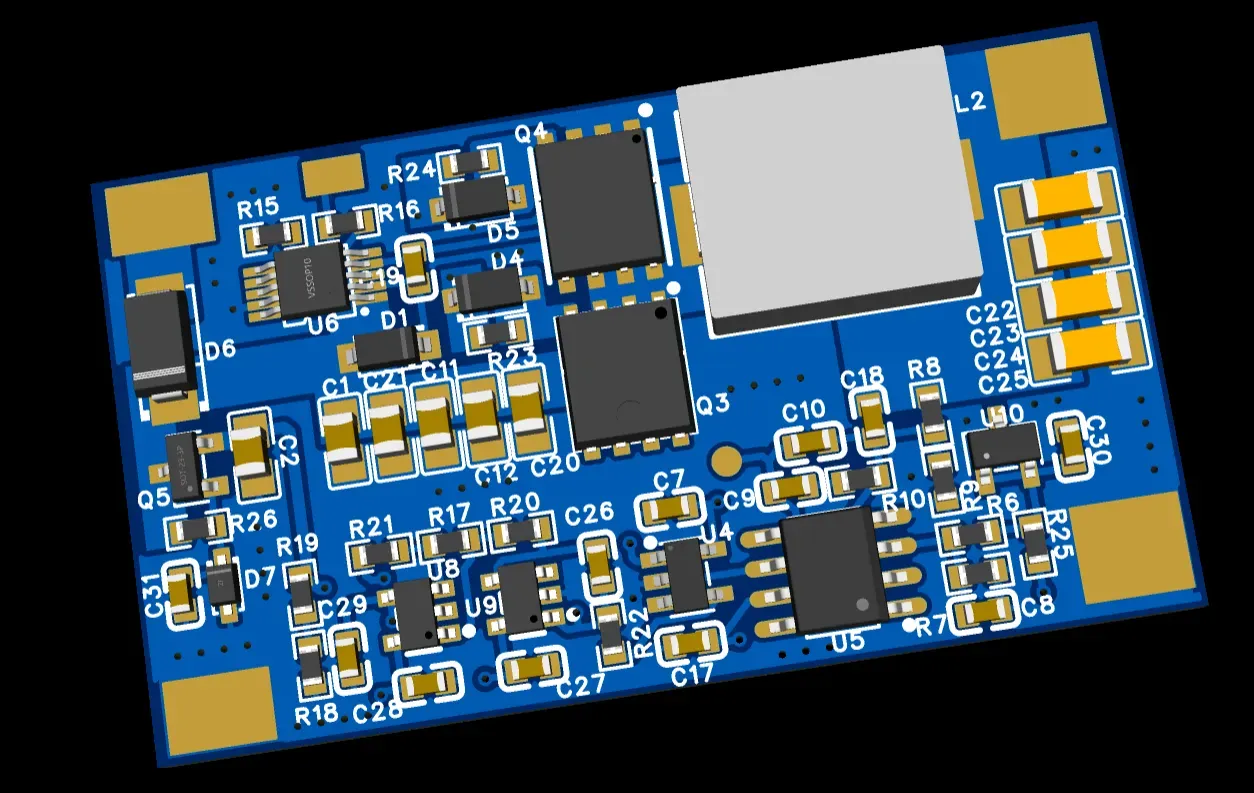

三,3D效果

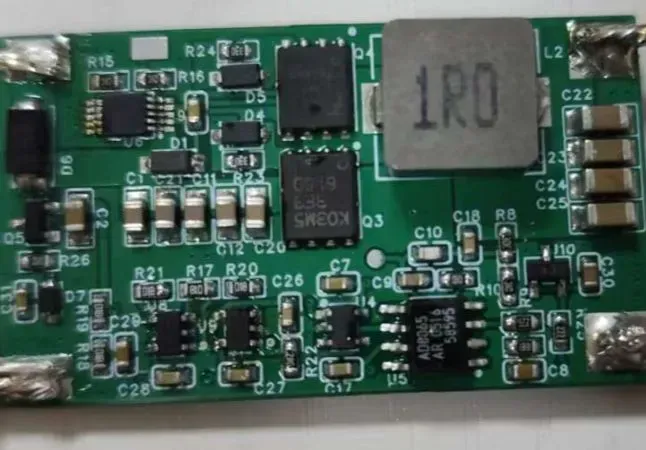

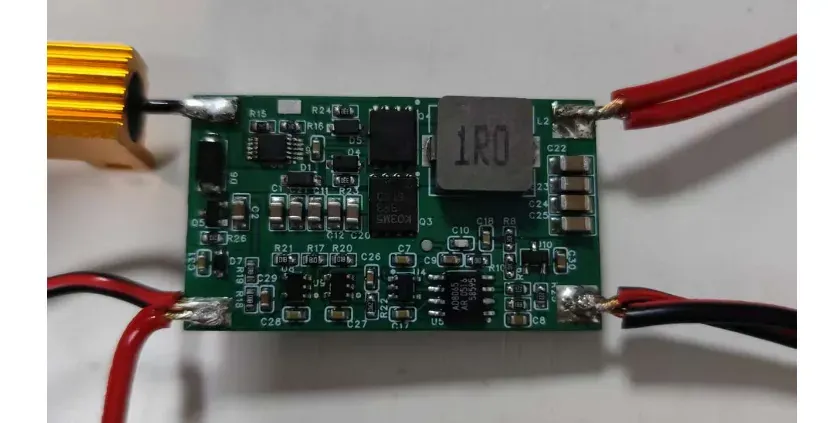

四,实物图

低温无铅锡浆,加热台焊接,能用,颜值为零。

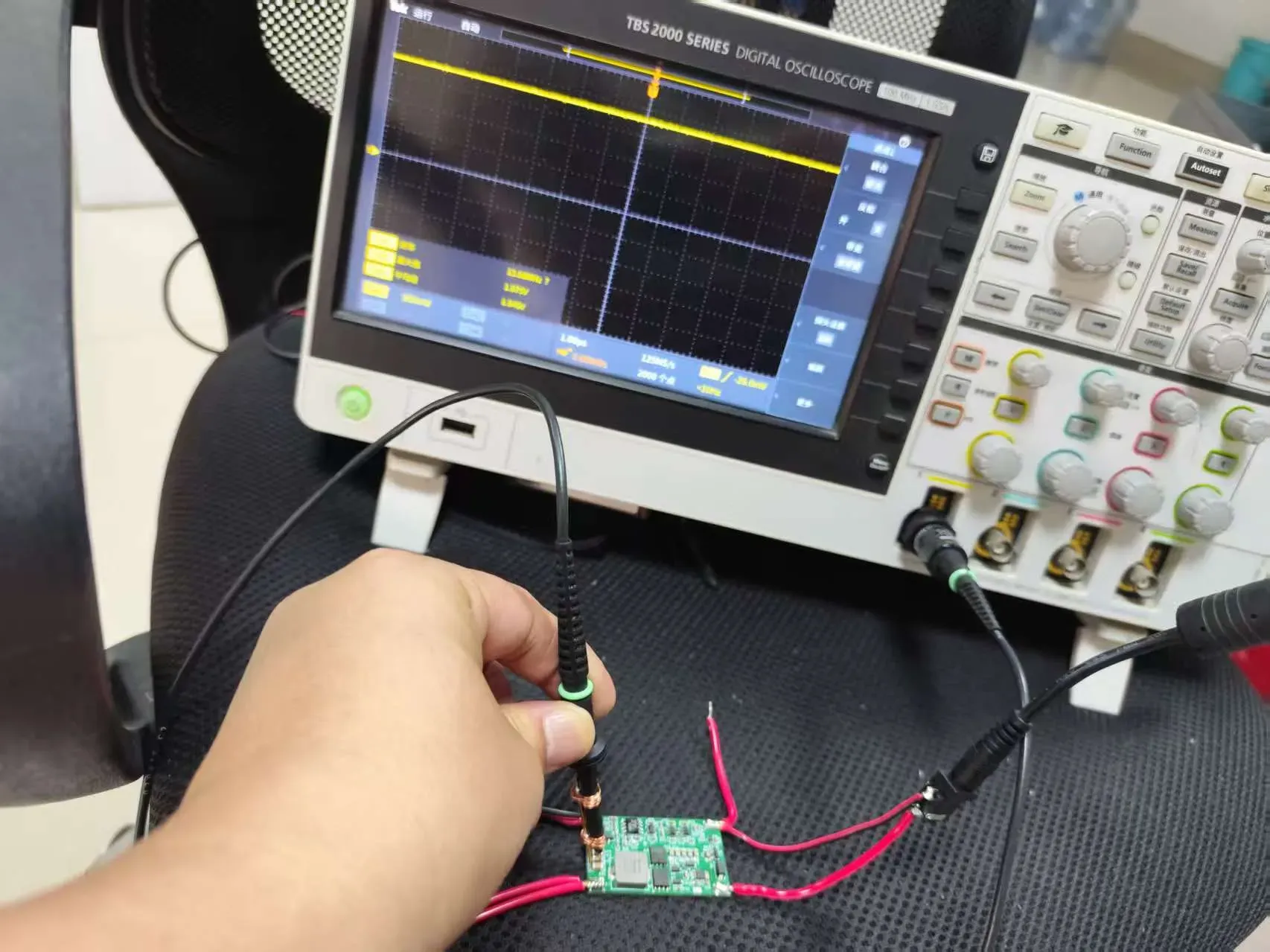

自制探头测试

五,测试结果

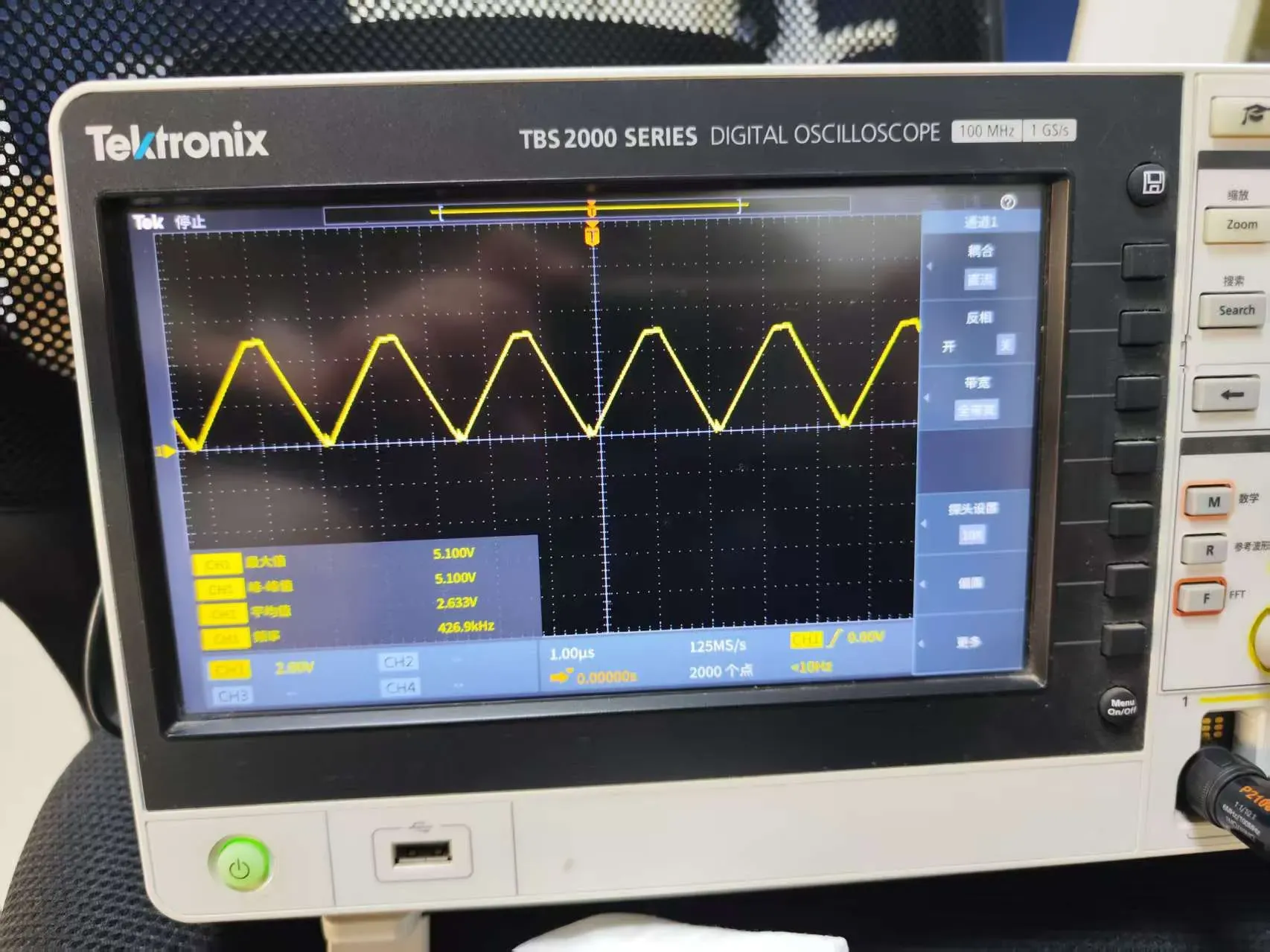

5.1 三角波测试

有点消顶了,能用,不完美。

5.2 带载测试

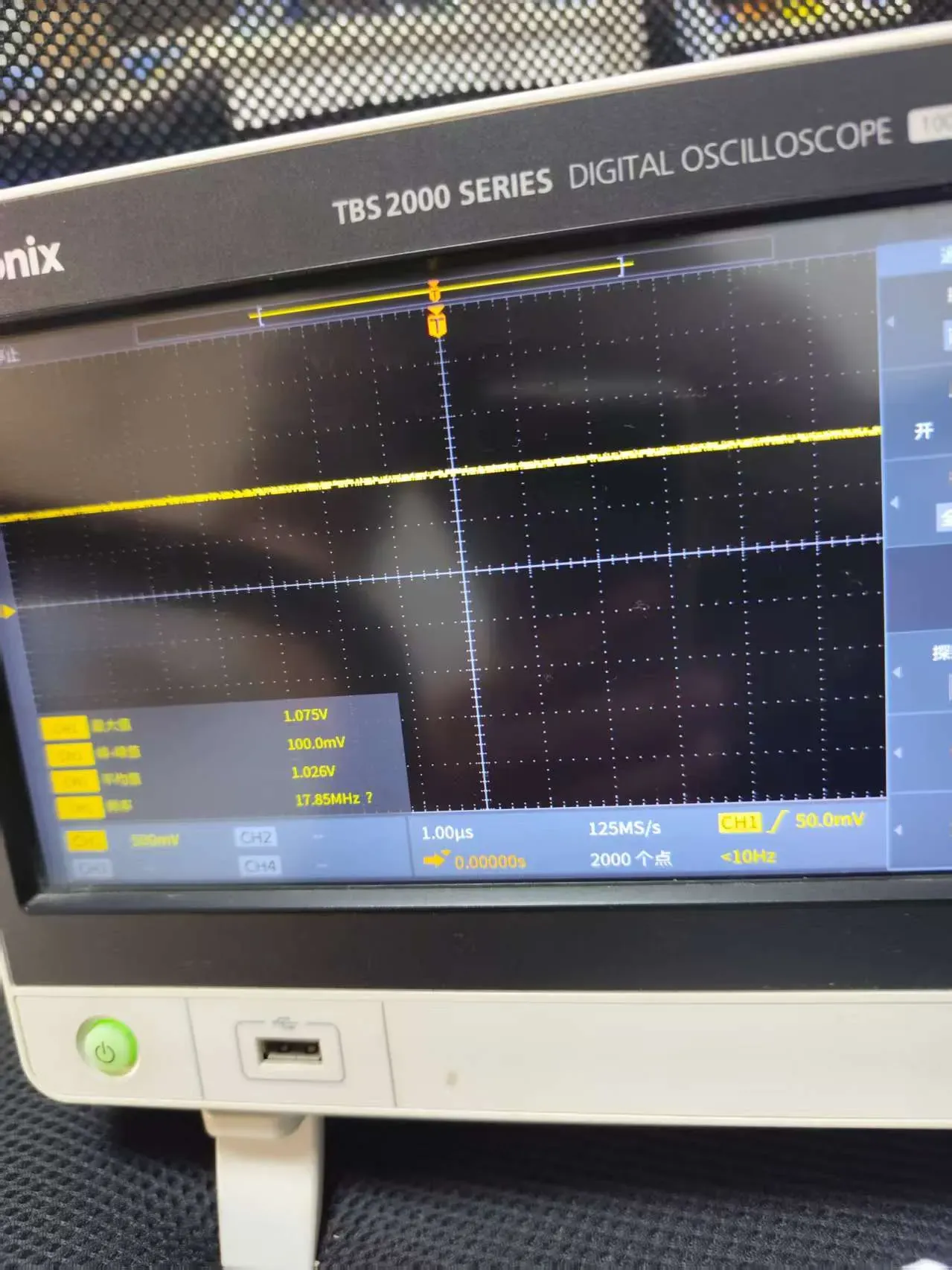

负载10A,输出1.02V,电压还是准的

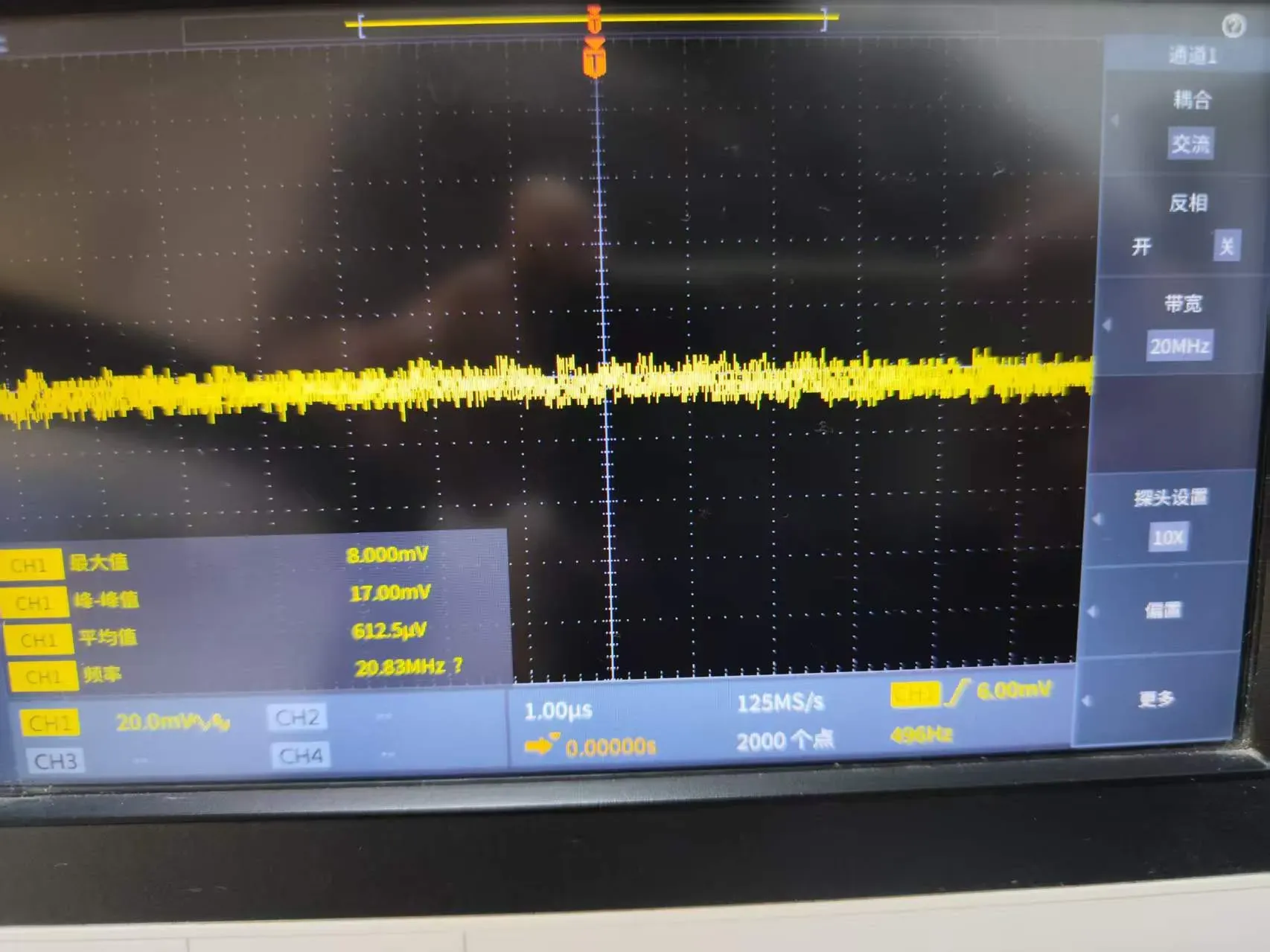

负载10A, 输出纹波不到20mV,效果满意

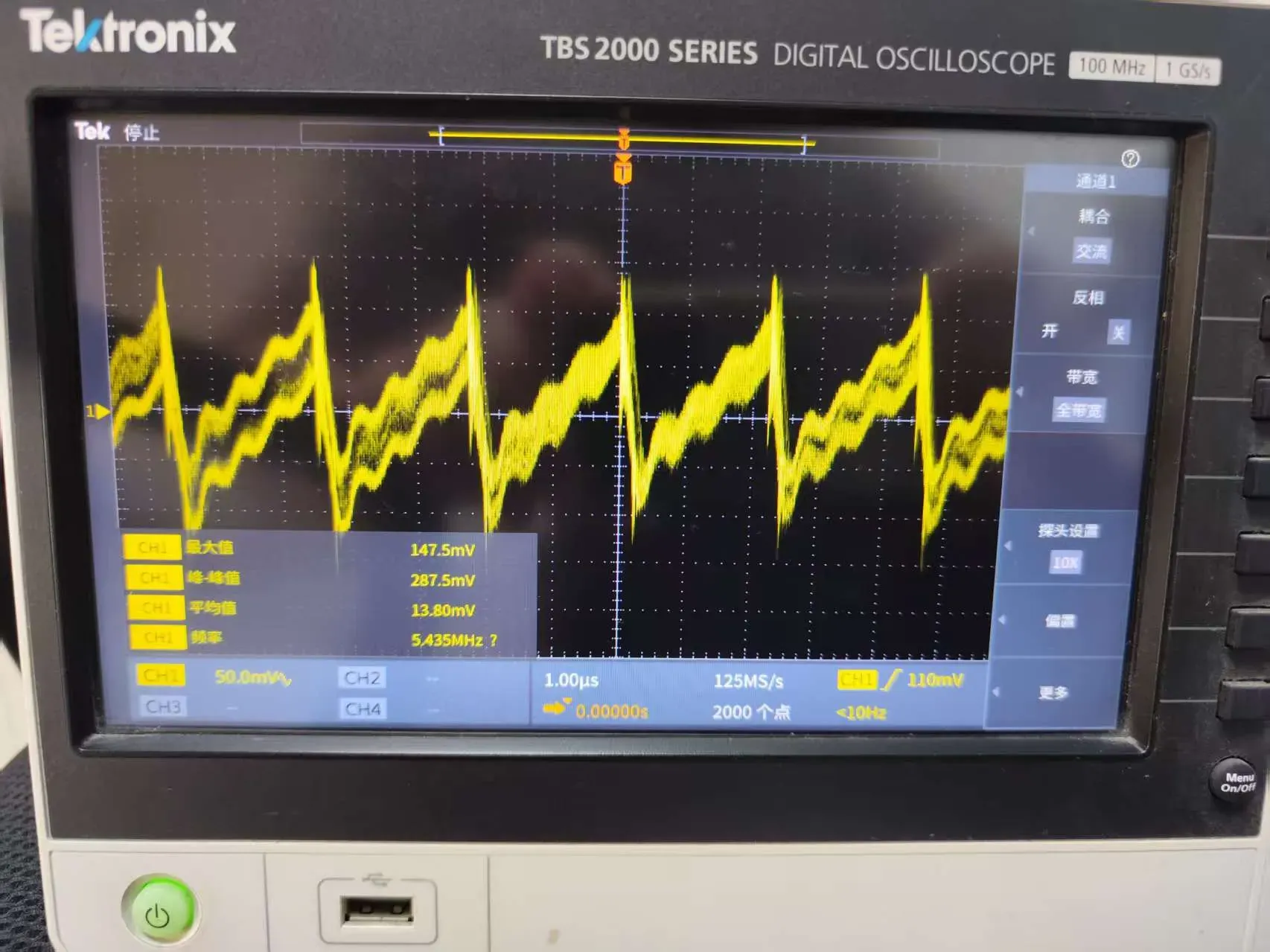

负载10A, 输入电压波动较大,效果不是很理想

一样的方法,测试了1V,负载5A;1.2V,负载6A;1.8V,负载9安。输出电压准度,纹波效果都不错,输入电压纹波随输出功率增大而增大,效果一般。

六,效率计算

这个实验中,电源串了一个SS56,本意是在电源接入时,防瞬态打坏后面低压的芯片,但也引入了额外的功率损耗,排除该损耗,输入电压从SS56后开始。

在1V,10A测试情况下,测试并计算得效率为82.7%;在1.8V,9A的情况下是87%。总体上,该电路在各种工况下,效率不低于80%。

七,费用计算

HRJK03M4DPA -> 拆机华为电源

FDMS7658AS -> 拆机华为电源

LM5106 -> 1元(TB)

LMV7219 -> 1.75元(TB)

GS8051 两个 -> 3.4元

TLV431A -> 0.12元

AD8065 -> 4.5元(XY)

100UF三星电容 4个- > 1.5元(LC)

打板5张共30元 -> 6元(LC)

BC817 -> 0.3元(LC)

SS56 -> 0.6元(LC)

1040功率电感:1.8元(LC)

单个板子成本控制在20元以下。

八,总结

基本上达到了学习的目的,掌握了DCDC降压芯片内部各部分的原理和功能。动态负载没有测试,电路有改进空间,忘大佬们指正。

设计图

未生成预览图,请在编辑器重新保存一次

未生成预览图,请在编辑器重新保存一次BOM

暂无BOM

暂无BOM 克隆工程

克隆工程知识产权声明&复刻说明

本项目为开源硬件项目,其相关的知识产权归创作者所有。创作者在本平台上传该硬件项目仅供平台用户用于学习交流及研究,不包括任何商业性使用,请勿用于商业售卖或其他盈利性的用途;如您认为本项目涉嫌侵犯了您的相关权益,请点击上方“侵权投诉”按钮,我们将按照嘉立创《侵权投诉与申诉规则》进行处理。

请在进行项目复刻时自行验证电路的可行性,并自行辨别该项目是否对您适用。您对复刻项目的任何后果负责,无论何种情况,本平台将不对您在复刻项目时,遇到的任何因开源项目电路设计问题所导致的直接、间接等损害负责。

评论