四层Artix7带DDR内存---FPGA摄像头开发板

简介

最近要调一些CMOS传感器,但苦于没有合适的FPGA开发板,于是寻思着自己做一个 主要针对使用了LVDS或者普通并行接口的传感器进行设计

简介:最近要调一些CMOS传感器,但苦于没有合适的FPGA开发板,于是寻思着自己做一个 主要针对使用了LVDS或者普通并行接口的传感器进行设计开源协议

:MIT License

描述

最近要调一些CMOS传感器,但苦于没有合适的FPGA开发板,于是寻思着自己做一个

主要针对使用了LVDS或者普通并行接口的传感器进行设计

因为是个很简单的四层板,在这里就简单说明下:

1. 芯片是XC7A35T-FTG256,该封装最大可上100T,但要自己修改供电以支撑芯片

2. DDR颗粒位宽为8bit,容量4Gb,运行在400MHz(800MT)下,保守估计理论吞吐量约为600~700MByte/s,足够很多图像传感器使用。

3. 与摄像头通信的Bank电压可调,1.8V、2.5V、3.3V任君选择

4. 使用一个60pin的BTB连接器与摄像头小板连接,BTB上的资源有:

10对LVDS(包括专用时钟线,其中9对等长),并且为LVDS预留专门的外部100欧电阻,当Bank供电不是2.5V时,就要用到外部100欧。

4条GPIO,用于传感器通信配置(设计失误了,忘记将电平转换器的电源连到可调电压的Bank上,因此只有固定1.8V,有需要的朋友可以自己修改)

2条同步信号线(垂直同步和水平同步)

5V供电接口

5. HDMI TMDS输出(注意,由于速度限制,该口无法输出全分辨率的摄像头图像,需要在FPGA内缩图后输出)

6. 板子上有CH340串口

另外,考虑到不少朋友拉DDR可能存在困难,这里我把DDR部分的走线单独提取出来做成了模板。有需要的可以直接把模板工程复制一份,然后在模板上开发即可。

尽管这是一个已经验证过的设计,但还是建议使用时再三检查!

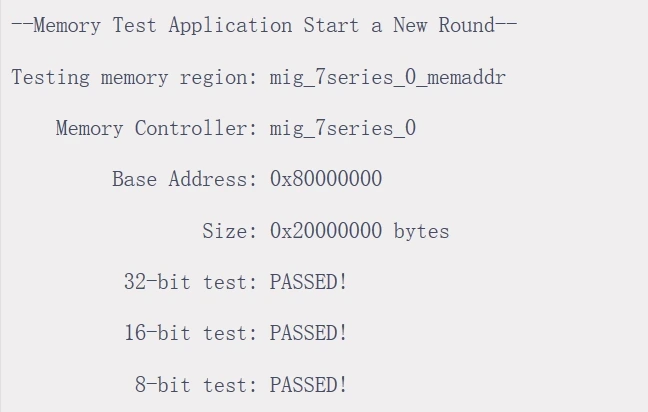

DDR3内存测试使用Microblaze完成,网上有很多教程,下面是测试结果:

已经过长时间压测,确保工作稳定

Note:如果发现自己的DDR内存校准过不去,可以先检查下焊接问题。在这个走线模板下,理论上只要颗粒参数选对了,校准就是一定能轻松过去的,毕竟就800MT/s,相比于电脑里动不动就几千MT的已经很慢了。我就是被焊接问题坑了,排查半天才发现BGA底下连锡。

已测试了三星和镁光的颗粒都没问题。

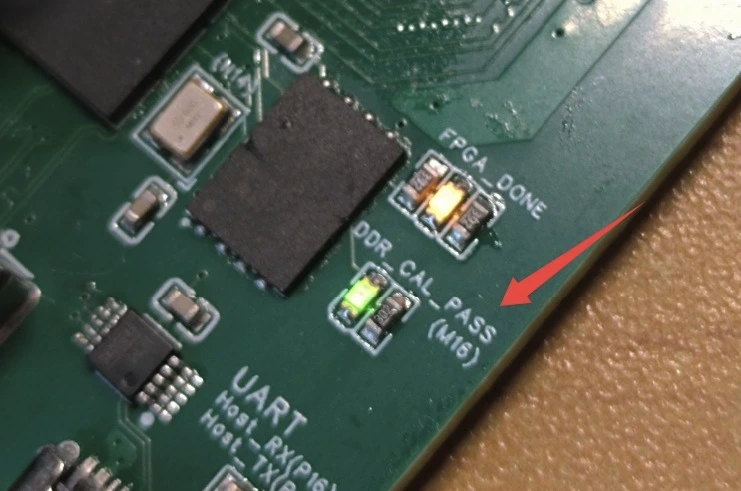

预留了专门的DDR校准通过指示灯

摄像头显示测试和HDMI测试正在进行中......

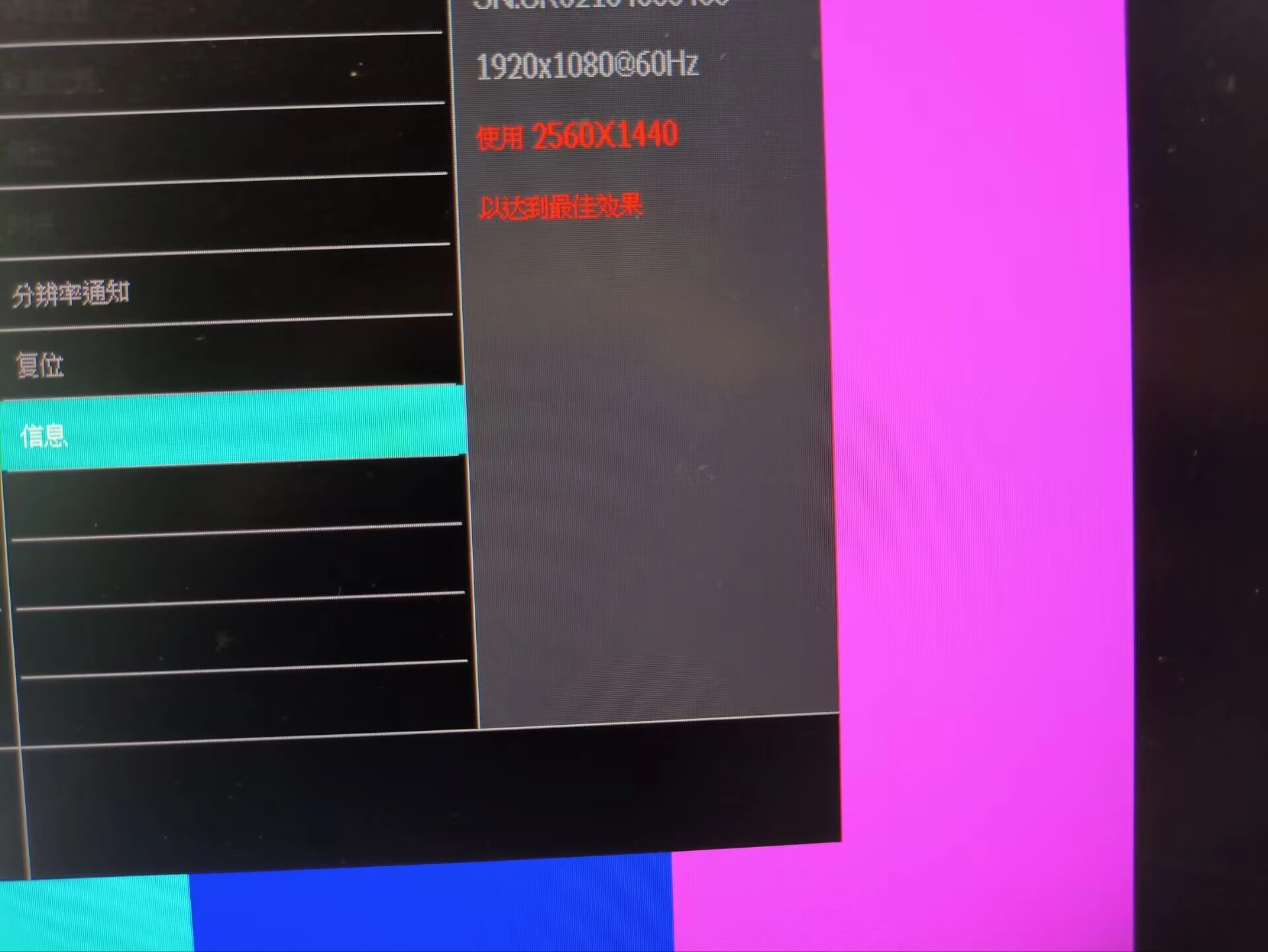

2025/6/9更新---HDMI测试通过

最高1080P60,但存在较严重的时序违例,建议降低至720p60使用

另外突然意识到自己忘记给HDMI口加ESD保护了,如果显示器接地不好或者运气比较差的话,有可能打坏FPGA

建议有需要的朋友自己加上HDMI的ESD保护管。

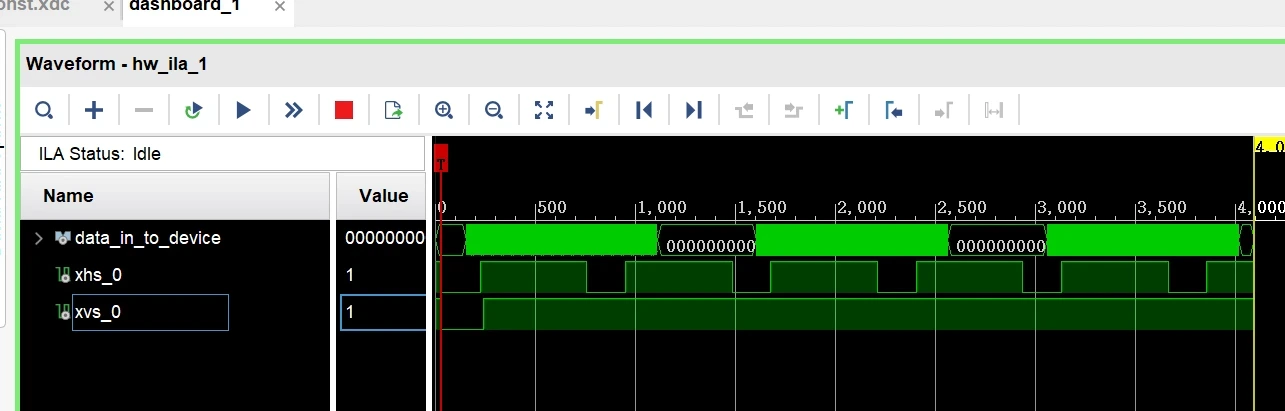

2025-7-18更新:LVDS输入测试成功

在摸鱼一个月后总算有动力重新拾起这个板子了,下面是LVDS采集的摄像头数据包。

由于摄像头板子还在开发中,这里就不公开板子的照片了,只展示ILA采集到的部分信号:

复刻注意:

本人画板比较随意,对于一些原件(例如退耦电容,上下拉电阻,DCDC分压反馈电阻)没有标注具体值,在焊接时,根据经验选用即可。

毕竟该板对制作要求不高,基本上只要不焊坏、焊短路都能跑起来)

设计图

未生成预览图,请在编辑器重新保存一次

未生成预览图,请在编辑器重新保存一次BOM

暂无BOM

暂无BOM 克隆工程

克隆工程工程成员

知识产权声明&复刻说明

本项目为开源硬件项目,其相关的知识产权归创作者所有。创作者在本平台上传该硬件项目仅供平台用户用于学习交流及研究,不包括任何商业性使用,请勿用于商业售卖或其他盈利性的用途;如您认为本项目涉嫌侵犯了您的相关权益,请点击上方“侵权投诉”按钮,我们将按照嘉立创《侵权投诉与申诉规则》进行处理。

请在进行项目复刻时自行验证电路的可行性,并自行辨别该项目是否对您适用。您对复刻项目的任何后果负责,无论何种情况,本平台将不对您在复刻项目时,遇到的任何因开源项目电路设计问题所导致的直接、间接等损害负责。

评论