Zeta拓扑电源变换器

简介

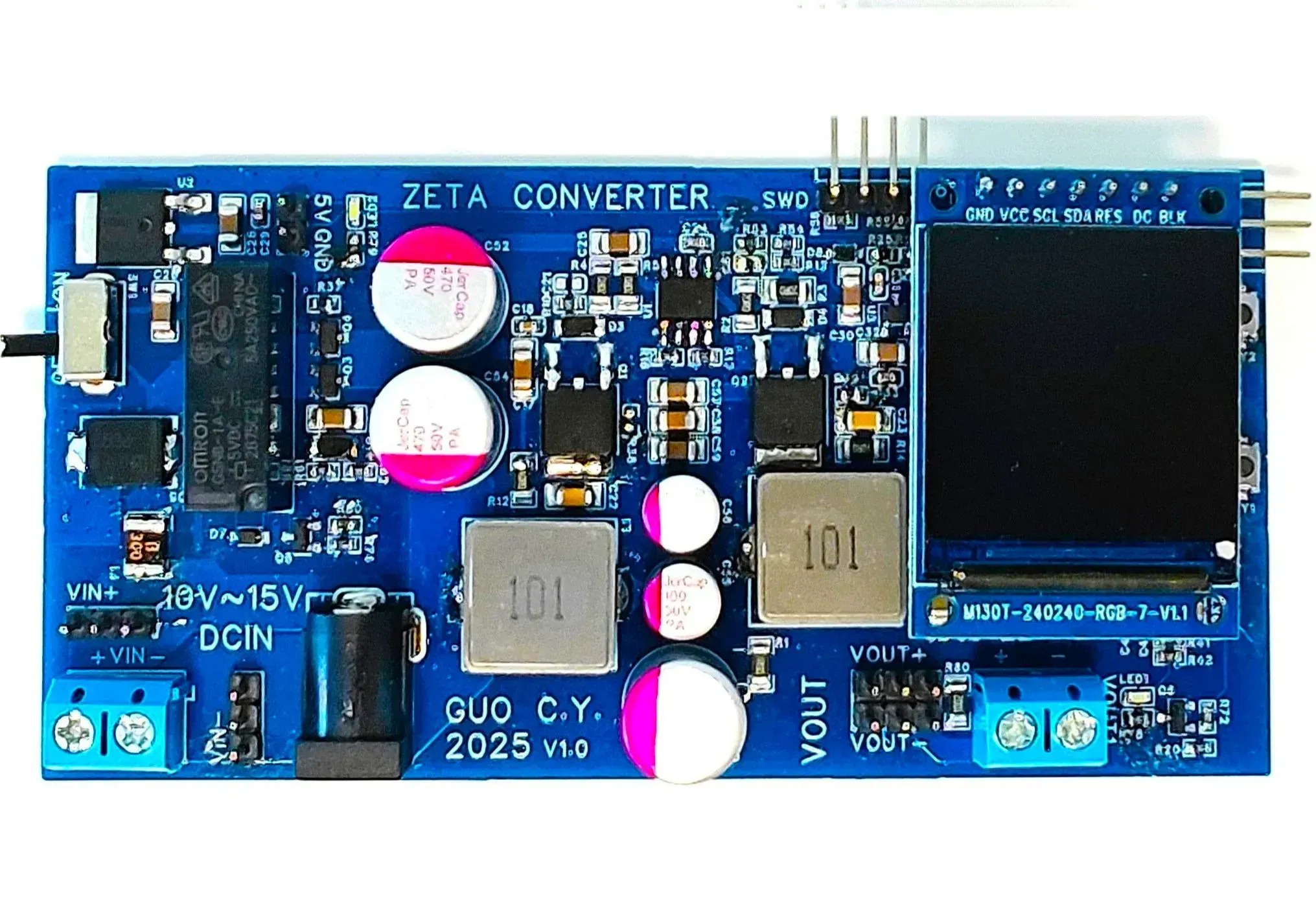

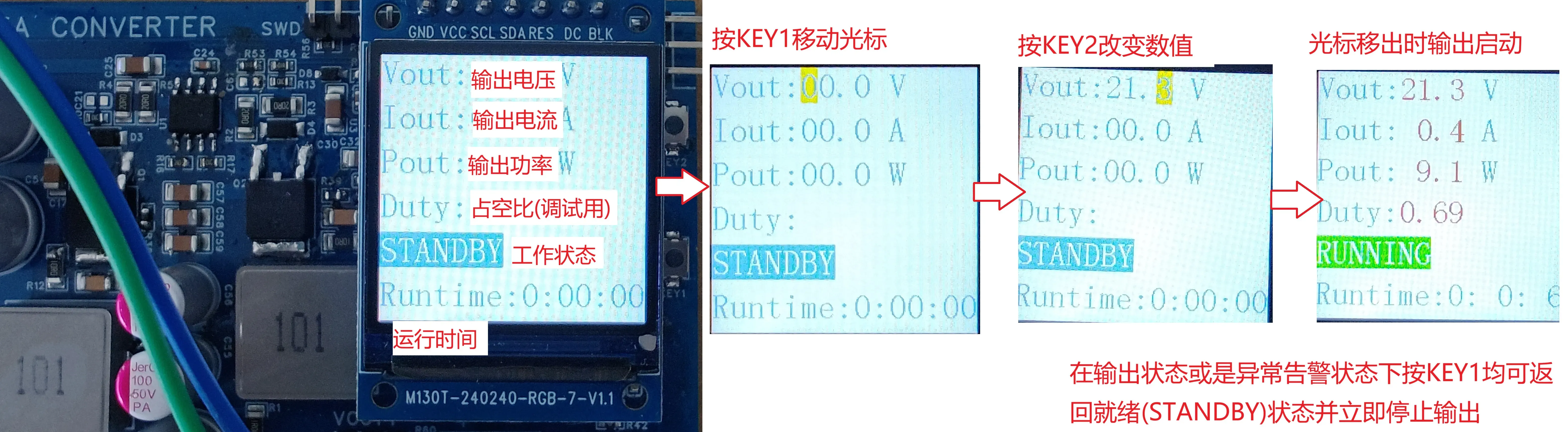

基于Zeta电源拓扑设计的3V-28V可调电源变换器,最大输出功率24W、输出电压精度1%、纹波占比<1%,STM32F103C8T6双路带死区PWM驱动,240*240LCD屏幕显示。

简介:基于Zeta电源拓扑设计的3V-28V可调电源变换器,最大输出功率24W、输出电压精度1%、纹波占比<1%,STM32F103C8T6双路带死区PWM驱动,240*240LCD屏幕显示。开源协议

:CC BY-NC-SA 4.0

描述

本项目由Chengyi Guo开源,请遵守开源协议。

一、简介

Zeta拓扑是一种相对不那么常用的DC-DC电源拓扑,可以实现对输入电压的升降压变换。Zeta拓扑相对于Cuk拓扑,输出电压极性与输入电压极性是同相的,相对于Sepic拓扑则能够取得更低的输出电压纹波。不过Zeta拓扑中使用到的是高边开关,实际工程中往往选用P型管而增加了成本。

二、工作原理

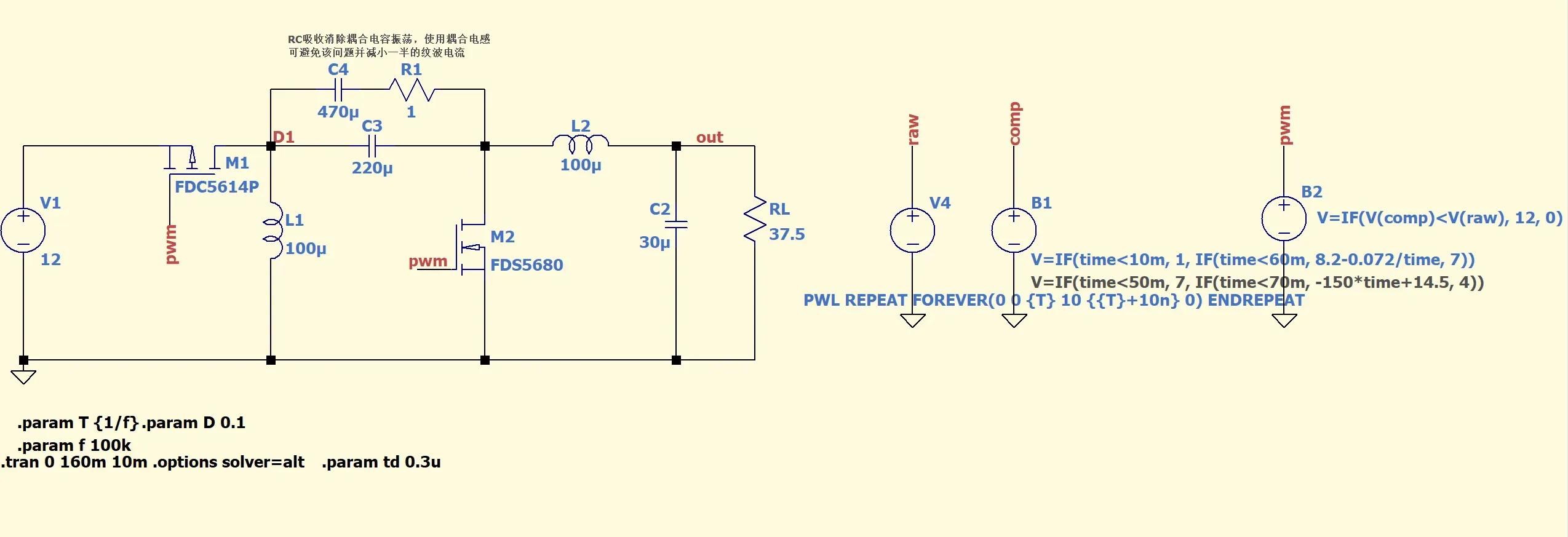

Zeta拓扑的设计已经十分成熟,本项目主要参考德州仪器应用笔记Designing DC-DC converters based on ZETA topology - Jeff Falin设计主功率回路。需要注意的是应用笔记中两个电感实际是耦合电感,好处是输出纹波更低但电感选型相对困难。本项目则使用的是两枚独立的功率电感,驱动频率100KHz,最大占空比80%,LTspice仿真电路如下:

(仿真文件详见附件)

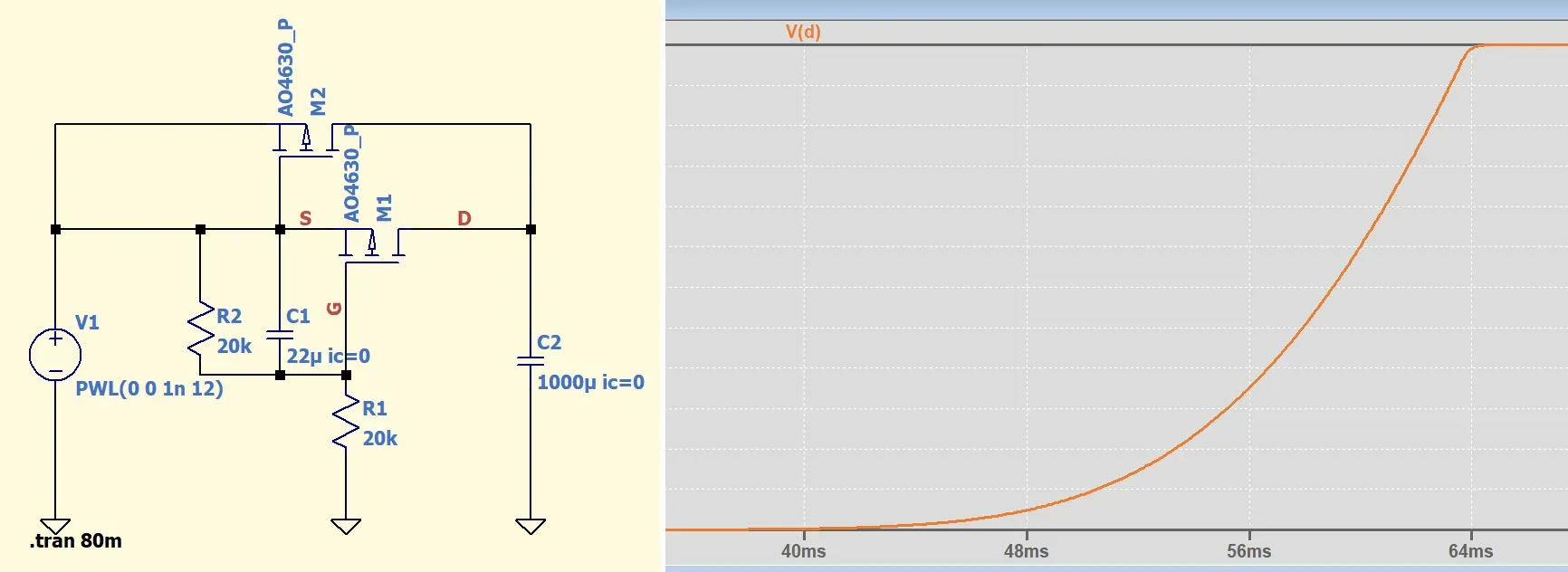

仿真电路中L1和L2参数具体可由电感的伏秒平衡关系式得到。设置工作于连续电流模式(CCM)对于L1有:

其中Δton为L1的充电时间,ΔI为电感电流纹波,K1为纹波系数一般可取0.2-0.4,IL1为L1的平均电流,假设L1、C3均为理想器件而C3满足安秒平衡则IL1等于输入电源Vin上的平均电流。同理,对于L2有:

![]()

其中IL2为L2上的平均电流,假设L2、C2均为理想器件,而C2满足安秒平衡则IL2即为负载上的平均电流。

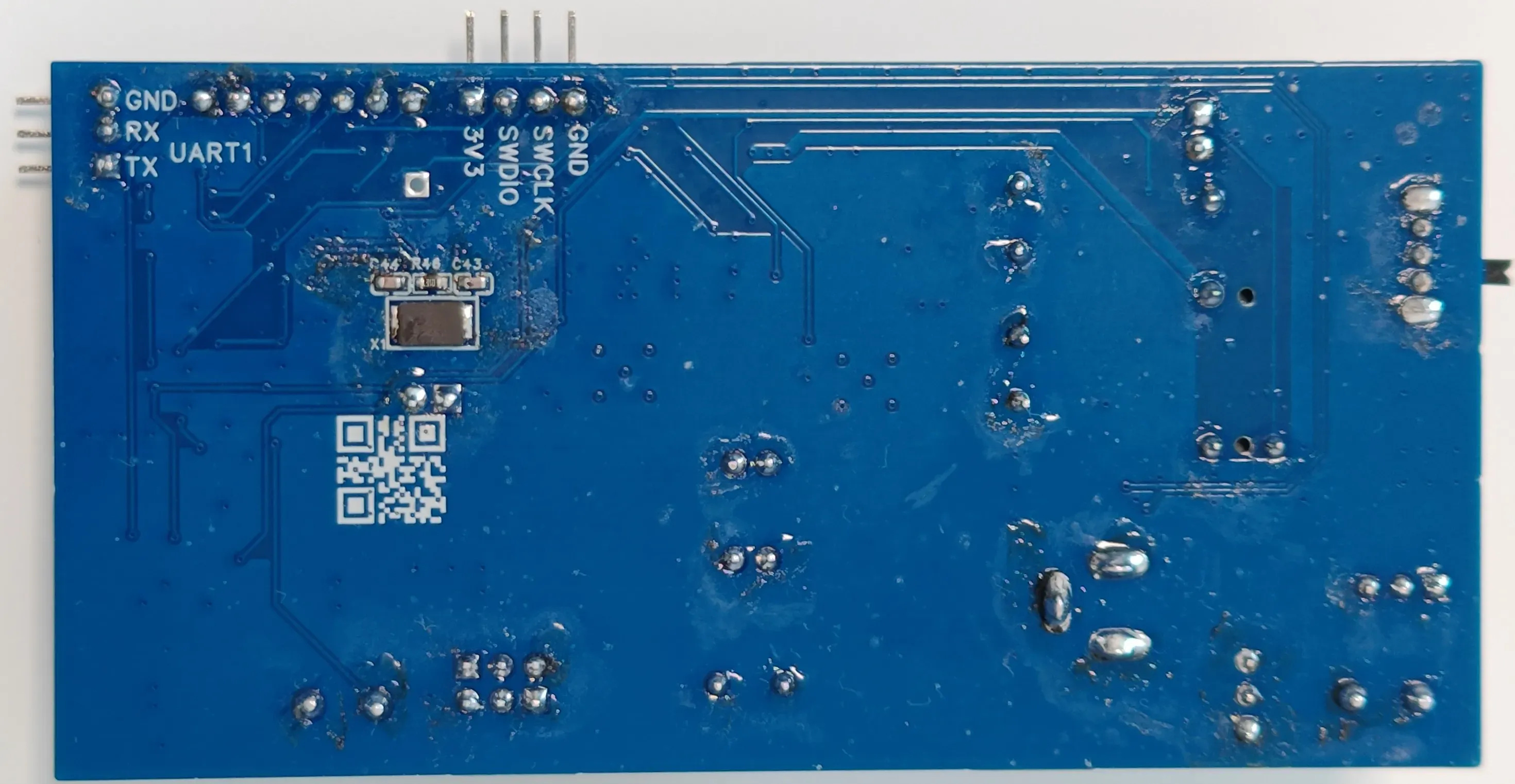

三、电路设计

电路原理图如下。

|

|

(1)主功率回路

自恢复保险丝F1和TVS管D5一起构成了输入接口保护。当后级短路电流超过5A则F1断开实现过流保护;当输入极性接反时,D5正向导通将后级钳位至管压降实现对后级的保护,而输入电源的电流超过5A时F1同样会断开实现对输入电源的保护;当输入电压超过15V时D5反向击穿对输入电压进行钳位实现过压/浪涌/静电保护。

RLY1为继电器,控制主功率回路的供电,D7为继电器线圈的续流二极管用于防止感应电压击穿驱动三极管Q5。

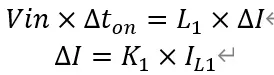

由于后级主输入电容C52、C54等总容量接近1000uF,若不接入软启动电路则在上电瞬间将产生极大的浪涌电流可能使输入电源保护动作或是出现故障。Q3、Q4、C20、R61、R62、D14则一起构成了硬件软启动电路,利用C20的电压钳位作用使得Q3、Q4栅极电压缓慢上升,Q3、Q4漏源极电流逐渐增大来实现软启动。调节C20、R62大小可以改变软启动时间,R61与D14则用于保护Q3、Q4的栅极。由于MOS管的导通电阻具有一定的正温度系数特性,因此可以简单并联使用进行扩流,仿真电路如下。

Q1为主开关管工作在硬开关状态,D3、R10、C21用于栅极保护。R4、R5为栅极电阻用于调节开关速度需要根据实际情况合理选取,过快的开关速度容易导致栅极振铃甚至出现二次开通现象极易烧毁MOS管同时也带来严重的EMI问题,过慢的开关速度则容易使MOS长时间停留在米勒平台带来严重的开关损耗导致发热严重。由于PCB走线电感(约1nH/mm)以及MOS引脚电感等的存在,开关脉冲电流会在上述寄生电感上产生振荡的感应电压造成MOS过压,同时感应电压还可以通过MOS管米勒电容等耦合到栅极上造成栅极振铃。由此使用R12、C22来对感应电压进行阻尼吸收,具体取值需要根据PCB布板布线情况进行考虑。Q2为副开关管用于替代原Zeta拓扑中的续流二极管,分析与Q1类似。

并联的C55-C59为主耦合电容,通过并联减小ESR并提升总容量,C53与R1则用于阻尼主耦合电容与L1、L2的寄生振荡。

并联电容C12-C16为主输出电容,同样通过并联减小ESR。R60为假负载用于泄放主输出电容上的电压同时提升空载电压的稳定性,R28为电流采样电阻。

(2)保护检测电路

R25、R26用于对输入电压进行1/5比例缩放,D8用于钳位输出电压最高不超过4V以保护ADC输入通道(类似作用还有D9、D10等),R29、C34、C35构成RC低通滤波并接入ADC采样通道。

R30、R31用于对输出电压进行1/10比例缩放,R32、C36、U4.1构成一阶有源低通滤波输出至ADC采样通道。若需要更好的滤波效果也可以使用二阶Sallen-Key低通滤波器。需要注意的是滤波截止频率以及滤波器阶数设置满足输出纹波滤除即可,过高阶数的滤波器工作不稳定同时还会带来较大延迟影响环路动态响应性能。

R33、C38、U4.2构成对电流采样电阻电压的RC低通滤波以及21倍放大并输出至ADC采样通道和U5.1反相输入端,其他分析同上。

U5.1、U5.2均为开漏输出比较器分别用作硬件过流检测和过热检测,输出线与后再由R73上拉接入单片机中断IO,由此单片机可配置为下降沿中断触发。R37、R38、R39均为NTC电阻,放置于Q1、Q2、Q3、Q4等位置用于温度监测,三枚NTC并联则逻辑上为“或”关系只要其中有一处温度过高就会拉低并联阻值从而触发U5.2电平翻转。触发阈值则由R42设置,本项目设置温度阈值在85度左右。NTC阻值与温度的对应关系可以由下式给出:

![]()

其中,R25为25摄氏度时的阻值、B由NTC数据手册给出、T以及T25分别为当前Rt阻值下以及R25阻值下对应的NTC开尔文温度。

(3)其他电路

U2、U3分别为5V线性稳压器和3.3V线性稳压器构成辅助电源用于实现输入电压到5V以及5V到3.3V的电压转换。5V主要给运放和比较器供电以保证足够的共模输入范围,3.3V主要给单片机和LCD显示屏供电。上电后打开SW1开关则单片机启动,再由单片机发出指令控制RLY1继电器吸合给主功率回路通电。

U6为STM32F103C8T6单片机按最小系统配置,输出双路带死区时间的PWM信号经过U1缓冲后用于驱动MOS管导通和关闭,单片机留有串口和SWD接口方便烧录调试,7针2.54排母连接LCD显示屏。本项目选用的显示屏是ST7789芯片驱动、SPI接口、240*240分辨率,某宝找同分辨率和驱动芯片的屏幕就可以使用,不过需要注意接口定义。

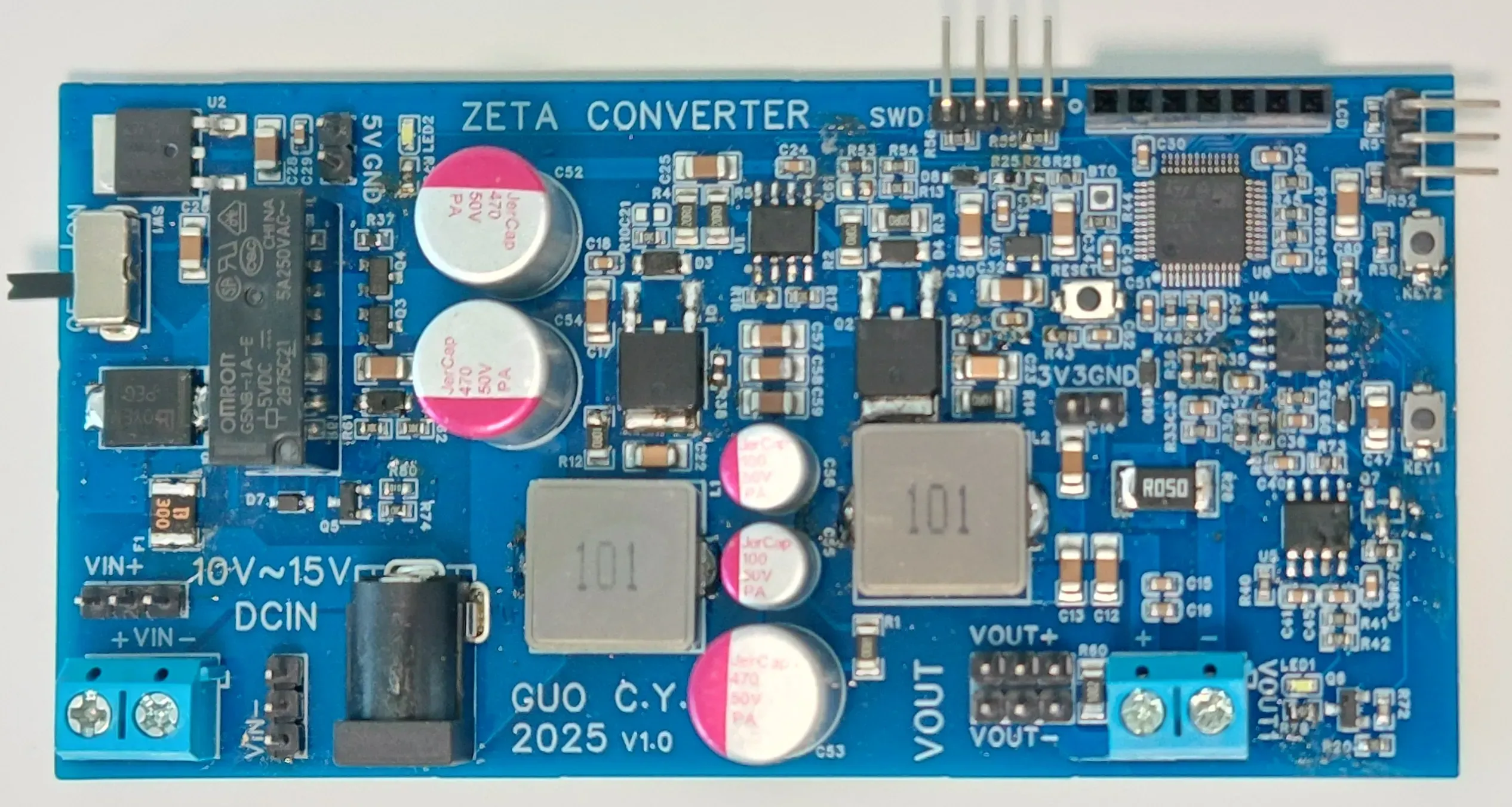

以上即为电路图中一些设计点的阐述,PCB设计上的考虑可以参考我之前的项目ZVT-Boost软开关电源,本项目PCB实物如下图所示。

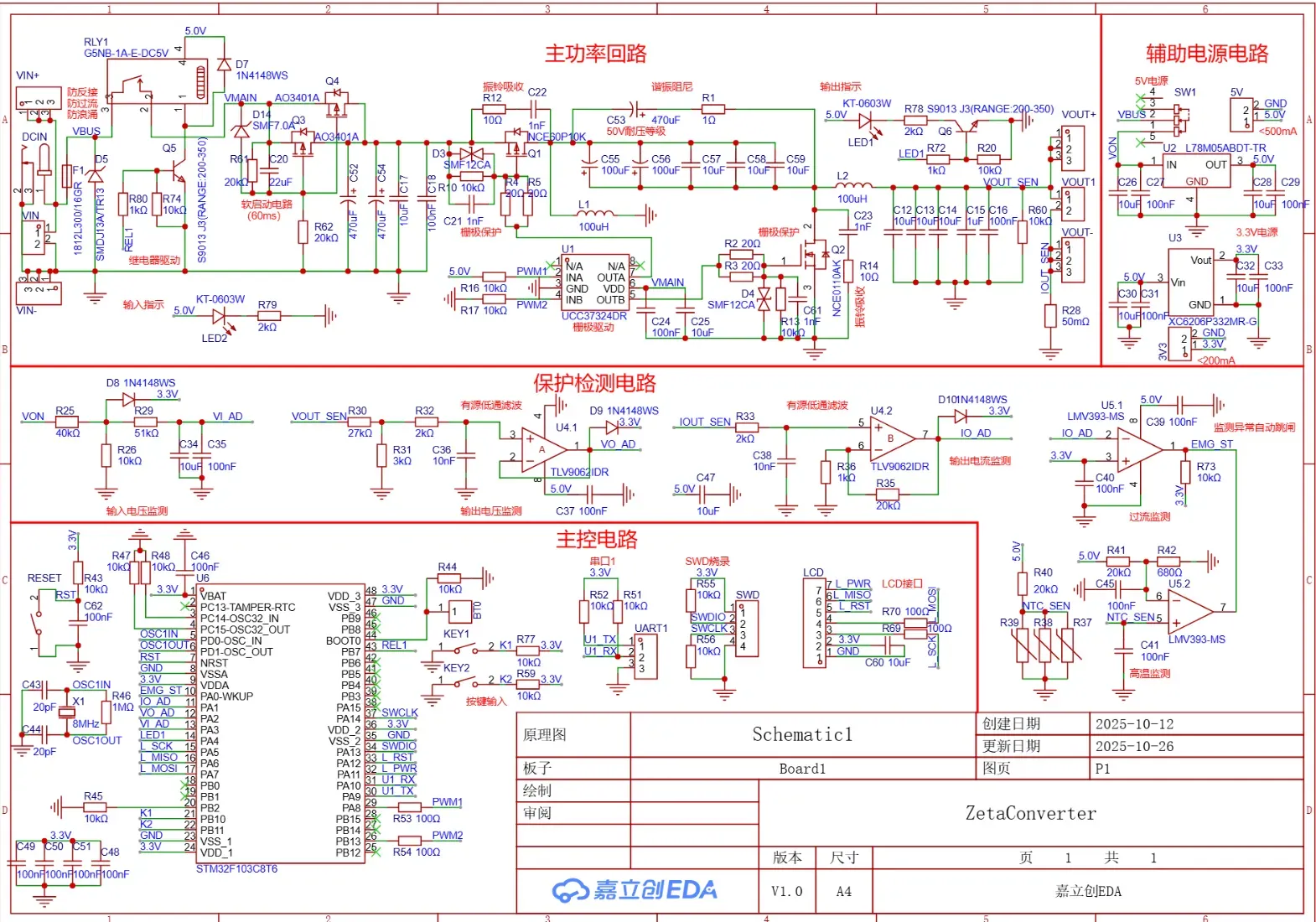

四、使用说明

连接好输入电源,拨动SW1打开辅助电源待屏幕下方显示“STANDBY”时即可使用KEY1、KEY2按键进行操作,操作流程如下图所示。

|

|

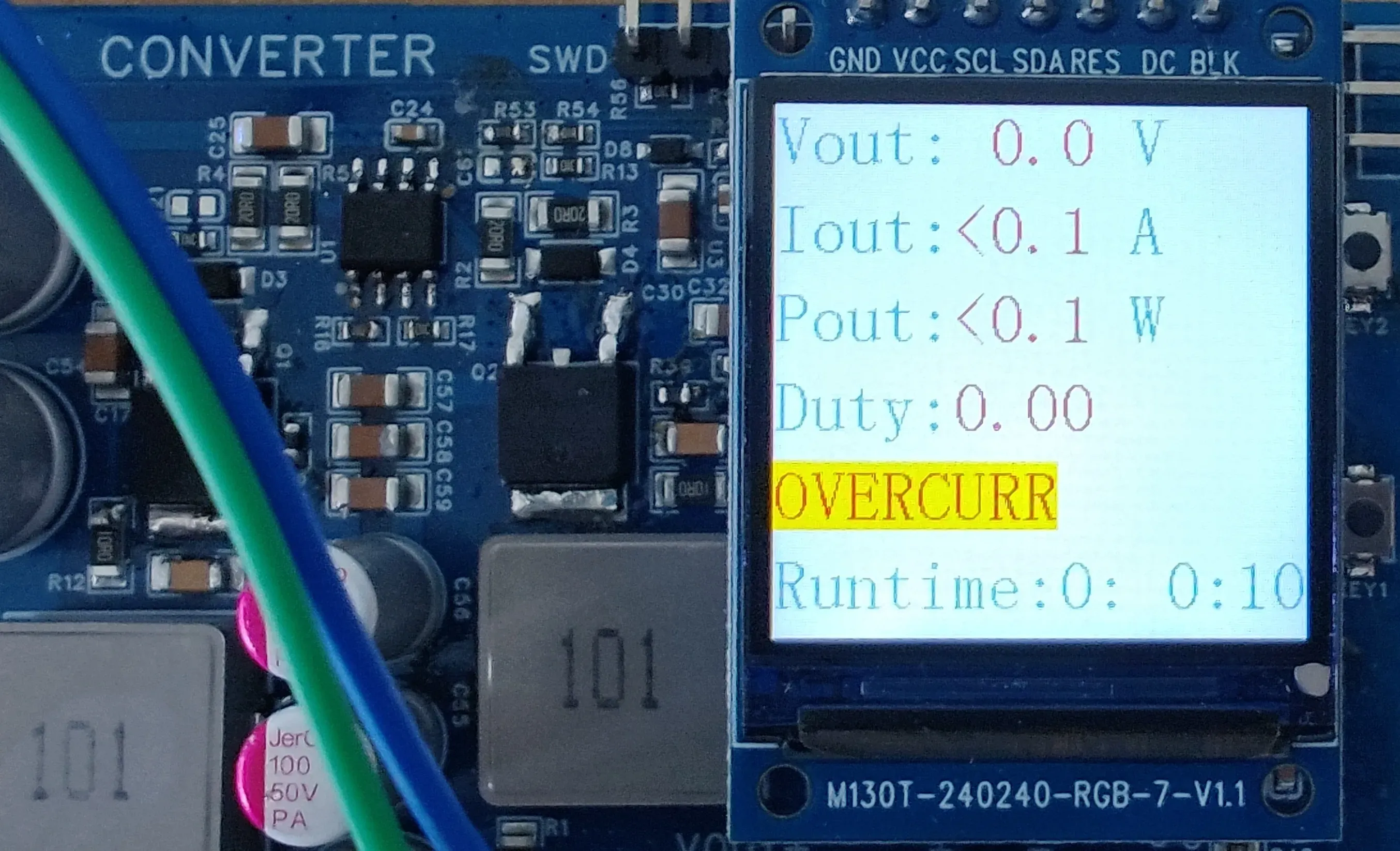

异常告警信息会通过工作状态栏进行显示,发生异常状态时输出立即停止,如下图所示。

|

|

异常状态信息包括以下几种:

|

异常状态 |

原因 |

是否自恢复 |

|

VIN_LOW |

输入电压低 |

否 |

|

VIN_HIGH |

输入电压高 |

否 |

|

UNK_ERR |

未知 |

否 |

|

OVERCURR |

输出过流 |

延时三秒恢复 |

|

OVERLOAD |

输出过载 |

延时三秒恢复 |

|

OVERCURR/OVERHEAT |

过热/输出过流 |

否 |

其中“OVERCURR/OVERHEAT”由比较器触发,响应速度远快于ADC采样后软触发的“OVERCURR”告警。设计上可以错开“OVERCURR”告警与“OVERCURR/OVERHEAT”告警的阈值实现多级保护。

五、整机测试

受限于测试设备只能进行一些简单测试。输出电压测试如下图所示,输出电压精度控制在<0.1V或1%以内。

|

|

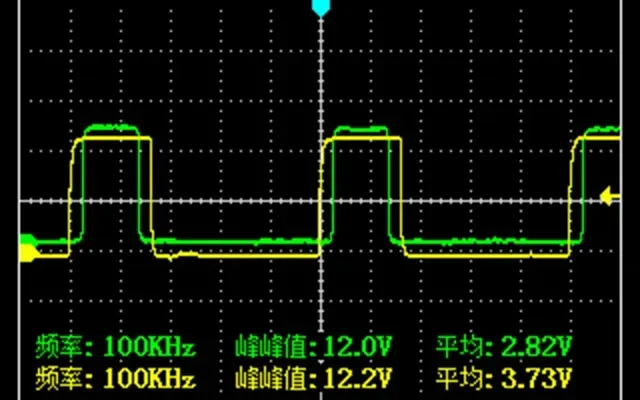

栅极驱动波形(输出满载)如下,黄色为主MOS波形、绿色为同步MOS波形,波形上升沿下降沿平整无振铃,驱动电流充足无明显米勒平台,死区时间约0.5us。

|

|

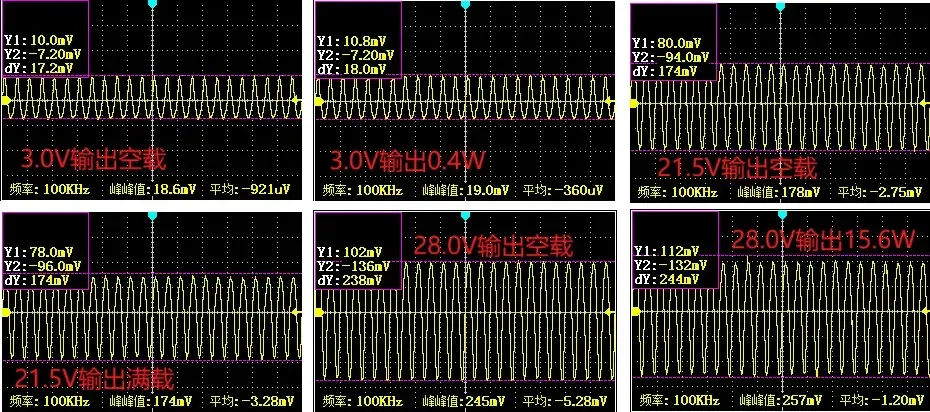

输出纹波测试结果如下图所示,纹波占比均在1%以内。

|

|

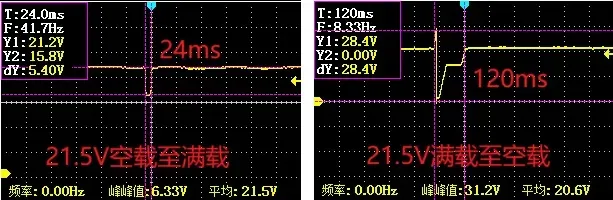

负载动态响应测试如下图所示,由满载至空载电压跌落明显,环路反馈性能差强人意。

|

|

六、经验总结

(1)使用单片机通过数字调制的方法来进行反馈控制非常依赖ADC的性能。本项目原计划实时采样电感电流来进行电流反馈控制,但是在100KHz驱动频率下ADC采样速率至少达到200KHz,对于STM32F103C8T6片上ADC来说难以实现,因此本项目最终还是采用了电压反馈控制方案。此外,由于在ADC采样和单片机程序运行的延时时间内电压输出已经能够达到稳定因此在电压反馈回路上没有再进行额外的环路补偿设计仅进行了简单的低通滤波,代价就是负载动态响应性能不佳。

(2)开关管的开关损耗估算和PCB散热设计考虑是必须的,本项目对于主MOS管的散热需求估计不足在满载输出时数分钟即触发过热告警,长时间使用则必须配置散热风扇。此外,LDO在高压差下工作时即使电流不大也要考虑发热问题。本项目使用78M05实现12V转5V电压0.1A电流输出时在78M05上会有约0.7W的功率耗散,用手触摸可感知明显发热。

设计图

未生成预览图,请在编辑器重新保存一次

未生成预览图,请在编辑器重新保存一次BOM

暂无BOM

暂无BOM 克隆工程

克隆工程工程成员

知识产权声明&复刻说明

本项目为开源硬件项目,其相关的知识产权归创作者所有。创作者在本平台上传该硬件项目仅供平台用户用于学习交流及研究,不包括任何商业性使用,请勿用于商业售卖或其他盈利性的用途;如您认为本项目涉嫌侵犯了您的相关权益,请点击上方“侵权投诉”按钮,我们将按照嘉立创《侵权投诉与申诉规则》进行处理。

请在进行项目复刻时自行验证电路的可行性,并自行辨别该项目是否对您适用。您对复刻项目的任何后果负责,无论何种情况,本平台将不对您在复刻项目时,遇到的任何因开源项目电路设计问题所导致的直接、间接等损害负责。

评论