ZVT-Boost软开关电源

简介

ZVT-PWM Boost变换器是一种改进于传统Boost电路的DC-DC电源拓扑,具有更小的发热、更高的效率以及更优的EMC性能。

简介:ZVT-PWM Boost变换器是一种改进于传统Boost电路的DC-DC电源拓扑,具有更小的发热、更高的效率以及更优的EMC性能。开源协议

:CC BY-NC-SA 3.0

描述

本项目由项目作者Chengyi Guo开源,请遵循开源协议。

ZVT-PWM Boost本质上也是一种升压型DC-DC电路,相对于传统Boost电路额外引入了副开关管并以副开关管硬开为代价换取原主开关管的软开和原主二极管的零电流关断。该电路拓扑在效率和EMC性能上优于传统Boost电路,但电路结构以及控制逻辑相对也变得更加复杂。本项目主要对ZVT-PWM Boost电路拓扑以及栅极驱动电路进行了验证,并基于STM32搭建算法平台实现完全可控的反馈控制过程。以下将从基本工作原理、硬件电路设计、软件控制设计、PCB设计、实验测试、项目总结等几个方面展开叙述。

一、基本工作原理

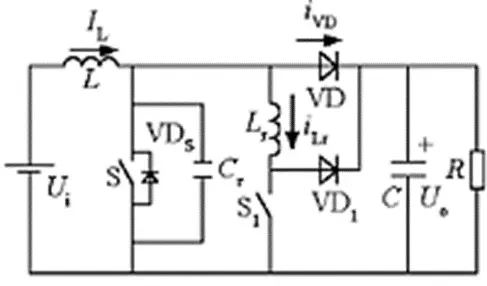

ZVT-PWM Boost变换器的基本拓扑如下:

相比于传统Boost电路主要多出副电感Lr、副开关管S1、副二极管VD1。主要工作过程如下:(引自零转换PWM电路-谢俊虎)

t0~t1时段:S1导通,VD尚处于通态,电感Lr电流iLr线性增长,VD中的电流以同样的速率下降。t1时刻,iLr=IL,VD中电流下降到零,自然关断。

t1~t2时段:Lr与Cr构成谐振回路,Lr的电流增加而Cr的电压下降,t2时刻uCr下降到零, VDS导通,uCr被箝位于零。

t2~t3时段:uCr被箝位于零,而电流iLr保持不变,这种状态一直保持到t3时刻S开通、S1关断。

t3~t4时段:t3时刻S开通时,其两端电压为零,因此没有开通损耗。S开通的同时S1关断,Lr中的能量通过VD1向负载侧输送,其电流线性下降,而主开关S中的电流线性上升。到t4时刻iLr=0,VD1关断,主开关S中的电流iS=IL,电路进入正常导通状态。

t4~t5时段:t5时刻S关断。Cr限制了S电压的上升率,降低了S的关断损耗。

概括来说副开关管S1的超前开通为主开关管创造了软开关条件,同时由于副电感Lr的存在使得副开关管虽然工作于硬开状态但开通电流上升速率受到限制,加之副开关管导通时间很短因此副开关管上的功率耗散实际并不高。

二、硬件电路设计

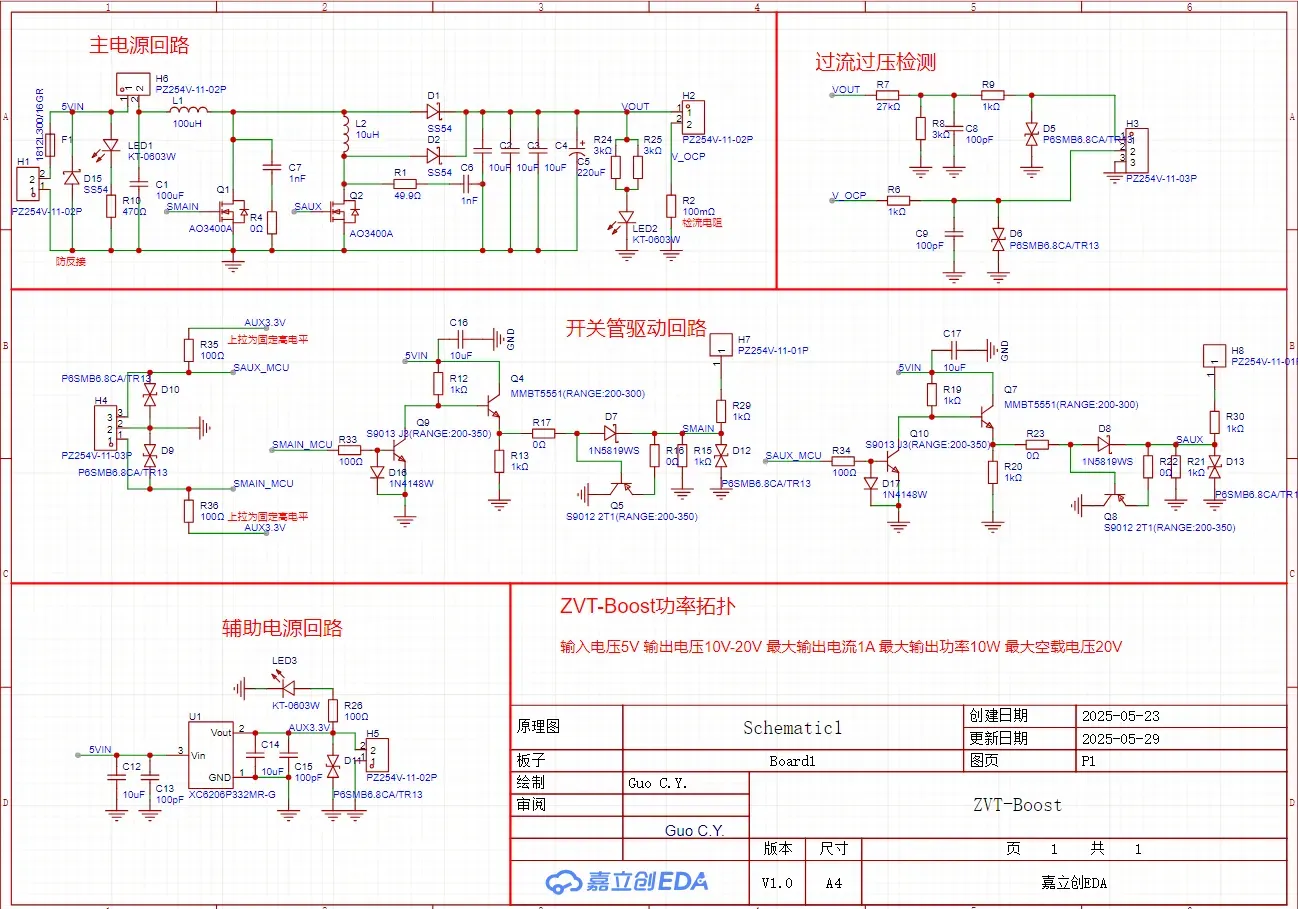

本项目电路图如下,主要分为主电源回路、开关管驱动回路、过流过压检测以及辅助电源回路几个部分。

其中,辅助电源回路主要使用LDO降压提供3.3V电压给STM32供电,如无该需求可以去除该部分电路并修改上拉电阻R35、R36为合适大小。

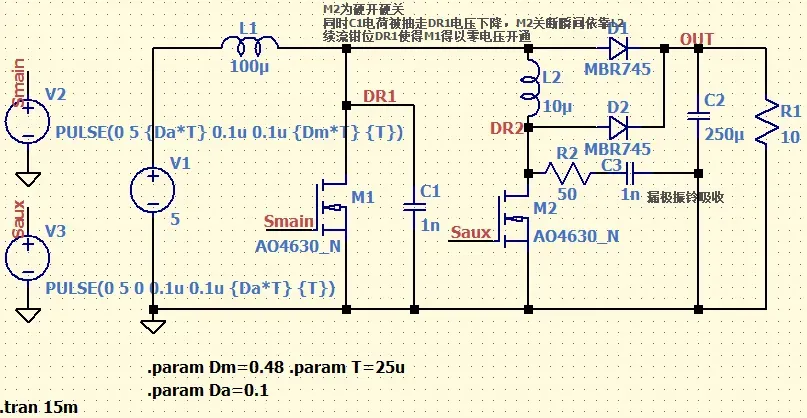

主电源回路中自恢复保险丝F1与D15用于实现防反接,R1与C6构成RC吸收电路用于吸收副开关管Q2漏极的振铃。其他主要电路参数计算可以先按传统Boost电路的计算方法进行估算(可参考升压转换器功率级的基本计算-Brigitte Hauke),再通过仿真进行调优。设置开关频率40KHz、副开关管占空比固定0.1、主电感纹波系数0.3、输出功率10W、输出电压10V、副电感取主电感十分之一大小,仿真电路如下:(详见附件)

各节点波形:

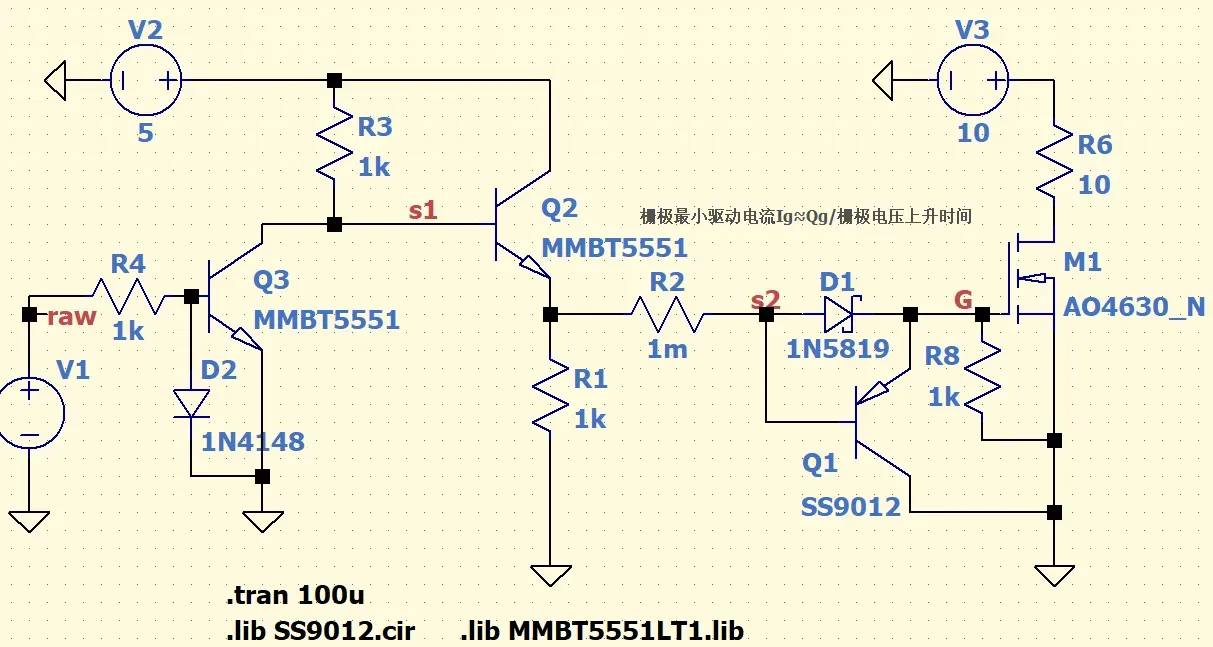

开关管驱动仿真电路如下图所示:(注意:该电路在18V供电下足以驱动一枚IGBT,对于驱动AO3400这类小功率MOS管来说驱动能力是过剩的本项目主要作为验证,实际可以简单使用一枚三极管做共集电流放大即可)

上述电路中Q3用于实现电平转换,共基或是共射结构均可。其中共射结构兼有电流放大能力因而对信号源带载能力要求更低但输出反相,共基结构则可以实现同相输出,共集结构没有电压放大能力无法实现电平转换。考虑到STM32输出PWM信号的极性可以方便地进行调整,因此本项目采用了共射结构。Q2与Q1则分别实现了“推电流”和“拉电流”,与常见推挽式输出最大的不同在于Q2和Q1并不同时受控于同一驱动信号,Q2受驱动信号控制实现“推电流输出”而Q1则是在Q2已经关断后由M1寄生电容电压触发导通而拉低栅极电压。由此,该电路从根本上杜绝了常见推挽式电路上下管“串通”问题的发生(读者可以自行仿真,无论上P下N型还是上N下P型三极管推挽输出均存在不同程度的“串通”问题,除非使用两路互补带死区时间的驱动信号控制)。不过该电路也存在输出低电平不为零(Q1存在饱和压降)以及下降沿偏缓的缺陷,更进一步的改进方案可以是Q1集电极改接负电压源。

事实上栅极驱动设计是十分讲究的,处理不好会出现栅极振铃等一系列问题,轻则EMI测试不过重则上电炸机,严谨的电路设计和参数计算可参考相关应用笔记ZHCA770、ZHCA637、AN978。本项目实际的原理图中也预留了R16、R17、R22、R23等0Ω电阻用于调节栅极驱动性能。此外,项目原理图中MMBT5551三极管可以直接替换为S9013,亦或者S9013替换为MMBT5551但需要根据输入PWM信号源驱动能力调节R33、R34、R35、R36为合适大小。

过流过压检测电路较为简单主要采集输出电压大小和输出电流大小,D5、D6为TVS管作端口防护,1k电阻与100pF电容作高频滤波,R2为电流采样电阻,R7与R8为电压缩放电阻缩放比例为十分之一。

三、软件控制设计

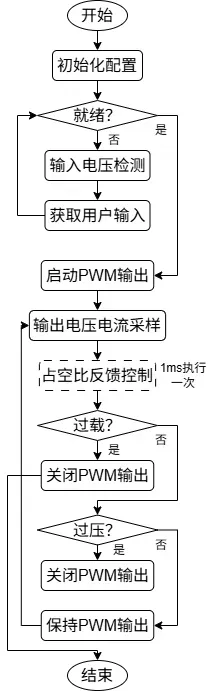

使用C语言基于STM32F103C8T6进行开发,主体逻辑框图如下:(忽略部分细节,详见附件代码)

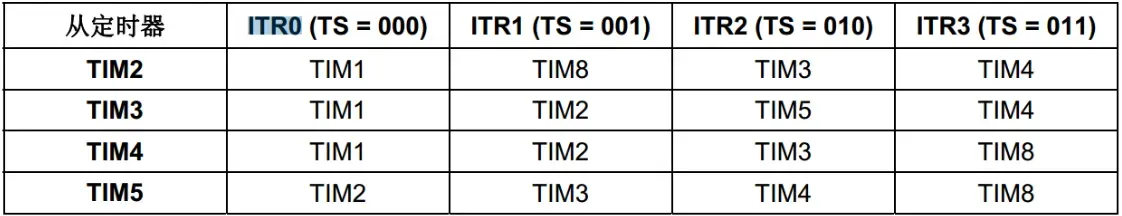

其中初始化配置包括ADC、串口、定时器等外设,以下重点说明定时器外设配置。由前文可知ZVT-PWM Boost拓扑需要两路驱动信号,副开关管信号超前于主开关管一个固定相位差,主开关管信号占空比要求可调。由此,对于STM32F103C8T6简单使用一个定时器的对称互补PWM输出是无法满足要求的。因此,本项目采用了TIM2、TIM3两个工作于主从模式的定时器来实现,其中主定时器为TIM3用于输出副开关管驱动信号而TIM2作为从定时器输出主开关管的驱动信号。主从模式下,主时钟对从时钟的触发无需占用系统中断因此可以大大节省CPU资源。对于主时钟的配置只需在正常初始化配置中加入如下代码:

TIM_SelectMasterSlaveMode(TIM3, TIM_MasterSlaveMode_Enable); // 启用为主定时器

TIM_SelectOutputTrigger(TIM3, TIM_TRGOSource_Update); //TIM3作为从时钟的触发源

类似地从时钟配置加入如下代码:

TIM_SelectSlaveMode(TIM2, TIM_SlaveMode_Trigger); //外部时钟源触发

TIM_SelectInputTrigger(TIM2,TIM_TS_ITR2); //触发源设置

TIM_SelectOnePulseMode(TIM2, TIM_OPMode_Single); // 单脉冲模式

其中TIM_TS_ITR2为TIM3对TIM2的触发连接通道,具体可以参考下表:

从定时器采用单脉冲工作模式主要是方便随时修改占空比,因为按照上述配置主时钟触发从时钟后只是启动计数而并不会对从时钟进行额外的复位或置位操作。特别注意的是在从时钟单脉冲模式下需要通过如下代码关闭“影子”寄存器否则修改占空比后无法正常输出PWM信号。

TIM_OC2PreloadConfig(TIM2, TIM_OCPreload_Disable);

TIM_ARRPreloadConfig(TIM2, DISABLE);

对于定时器输出PWM信号的启停操作在不修改占空比的情况下可以简单地通过强制修改GPIO口输出状态来实现,此外也可以通过修改定时器工作状态来实现,如下代码所示:

TIM_SelectOCxM(TIM2,TIM_Channel_2,TIM_ForcedAction_Active); // 强制输出PWM信号为高电平

TIM_CCxCmd(TIM2,TIM_Channel_2,TIM_CCx_Enable); // 使修改生效

TIM_SelectOCxM(TIM2,TIM_Channel_2,TIM_OCMode_PWM1); // 恢复PWM输出

TIM_CCxCmd(TIM2,TIM_Channel_2,TIM_CCx_Enable); // // 使修改生效

不过笔者发现使用上述代码恢复输出后的PWM信号第一个脉冲长度存在异常(不确定是否为个例),因此本项目还是采用了直接控制GPIO输出的方案。

流程图中占空比反馈控制是指使用某种算法根据反馈的输出电压等信息对主开关管的占空比进行调节,本项目中占空比调节每1ms才执行一次主要是为了避免占空比短时间内的快速变化而导致的电感电流浪涌以及输出电压波动。然而,过于迟缓的反馈调节也会导致较差的负载动态响应性能,因此反馈控制速度是需要根据实际使用情况进行权衡的。作为示例,本项目使用控制算法就是简单的单环PID控制,反馈量是采样输出电压输出量是以0.005为单位量化后的占空比(详见附件代码)。当然,读者也完全可以自己编写反馈控制算法,可以引入更多的反馈量实现更精细的控制还可以使用PFM等其他方式进行控制等。

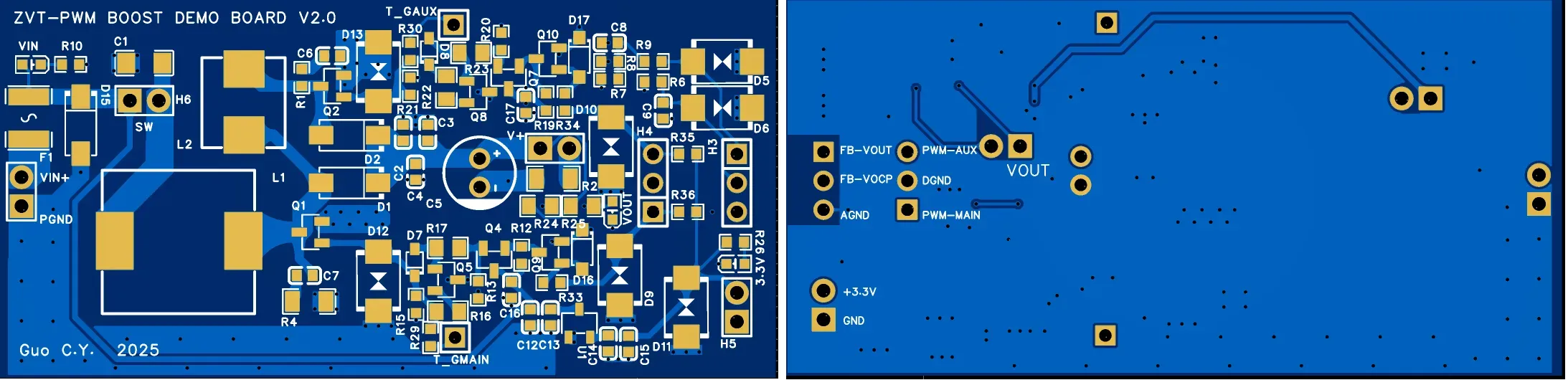

四、PCB设计

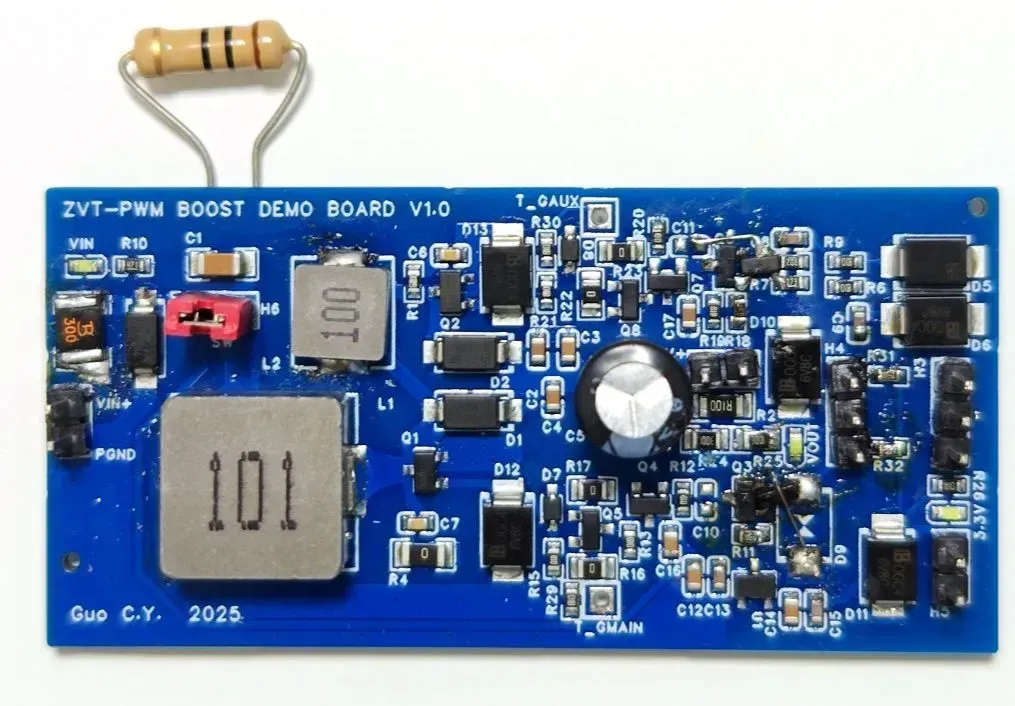

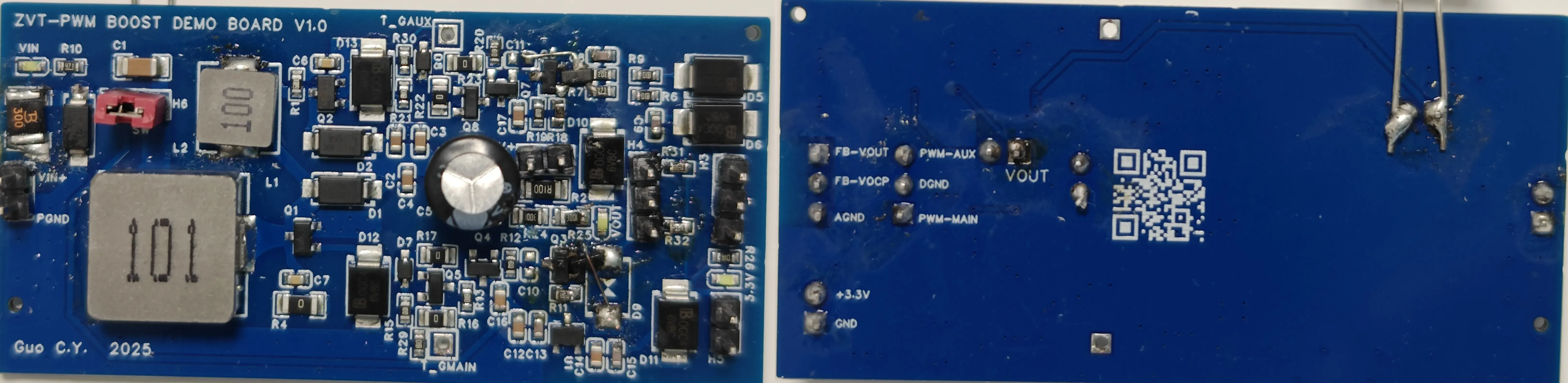

本项目PCB基于双面板布局布线,长68.3mm、宽33.3mm,如下图所示。

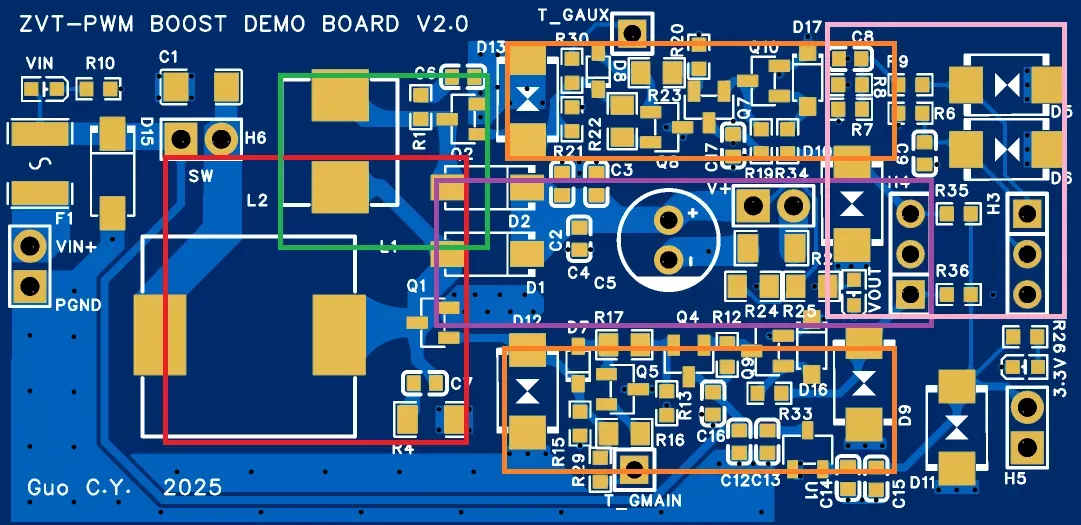

常见的PCB设计规则繁多,例如3W原则、20H原则等,本项目PCB设计时主要还是考虑以下几点:

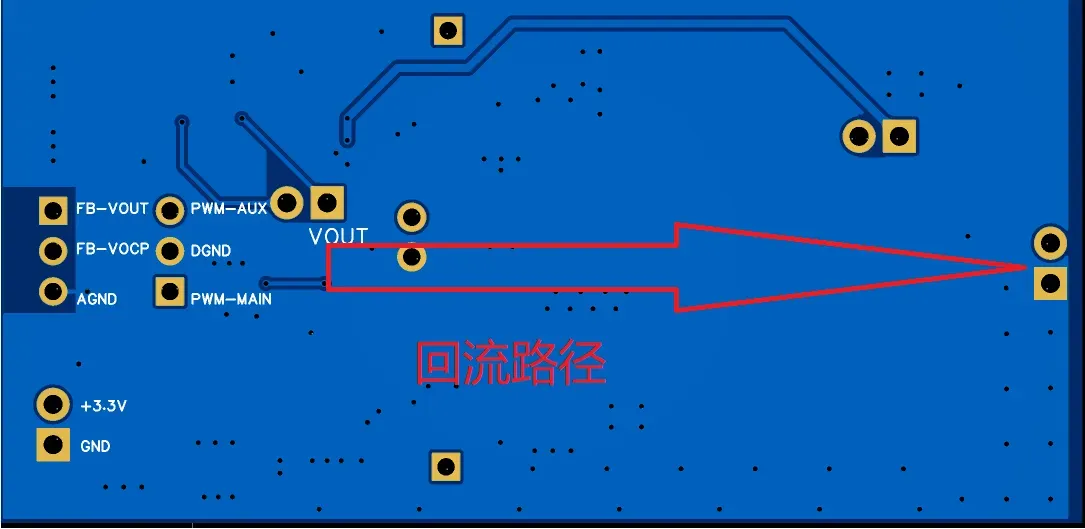

1、背面完整铺铜正面走线,以此提供一个完整的地回流路径(尤其是对于高频噪声),即使背面有少量走线也避免割断由VOUT指向VIN的回流通路。

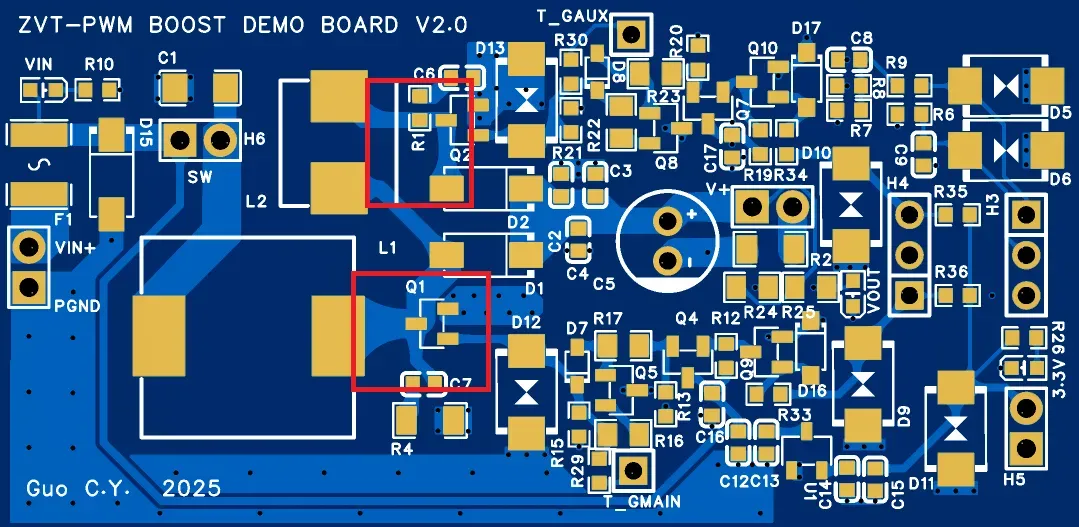

2、布局上尽量缩小主电感回路面积(辐射)、副电感回路面积(辐射)、栅极驱动回路面积(栅极振铃)、输出端口回路面积(噪声)、采样回路面积(噪声),以减小辐射和耦合干扰问题。

3、保证载流能力兼顾散热能力的情况下尽量缩小主开关管漏极节点铜皮面积、副开关管漏极节点铜皮面积。这两个节点存在快速的电位变化即所谓的“动点”,减小动点面积可以减小与大地间的寄生电容进而减小共模噪声。

4、布局上适当增加主副电感与周围器件的间距以方便手工焊接和散热。

项目PCB实物如下图所示。

五、实验测试

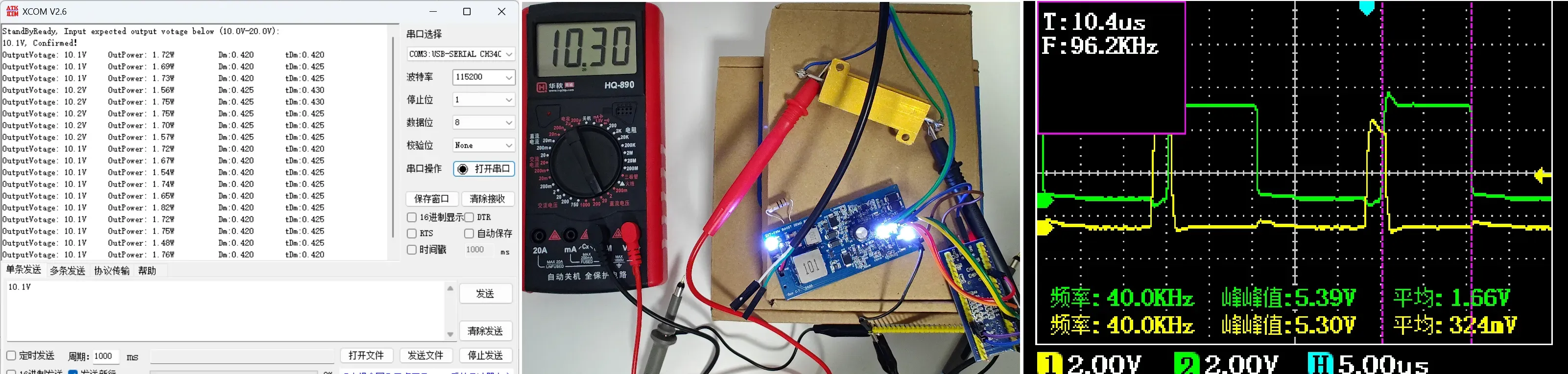

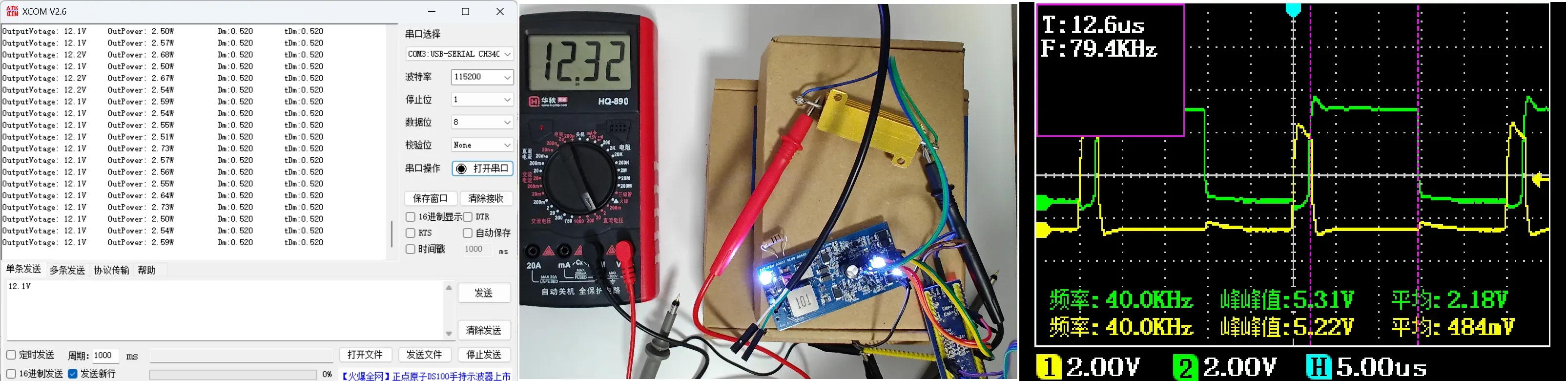

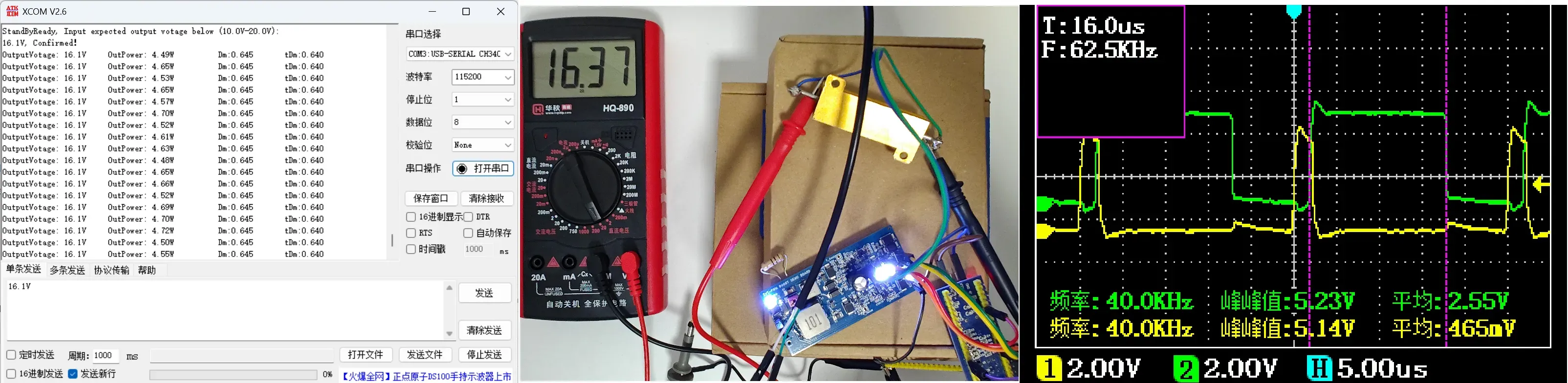

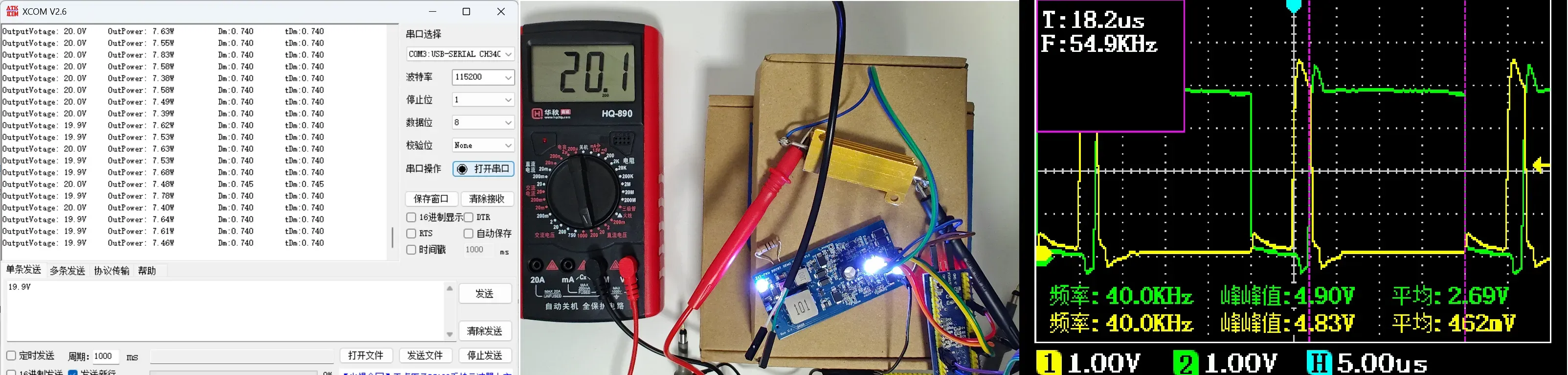

首先简单介绍操作方法。上电前检查所有连接线:STM32F103C8T6的PA9、PA10正确连接到串口上位机;PA7连接到PWM-AUX、PA1连接到PWM-MAIN;PB0连接到FB-VOUT、PB1连接到FB-VOCP;连接好负载(不要空载)以及各路电源线和地线;打开串口上位机;上电后按串口提示操作即可。以下测试均在50Ω(50W铝壳电阻,注意防烫)负载下进行,测试图片从左到右分别为串口上位机显示输出、实测电压、主(绿色)副(黄色)开关管栅极波形。

10.1V输出:

12.1V输出:

16.1V输出:

19.9V输出:

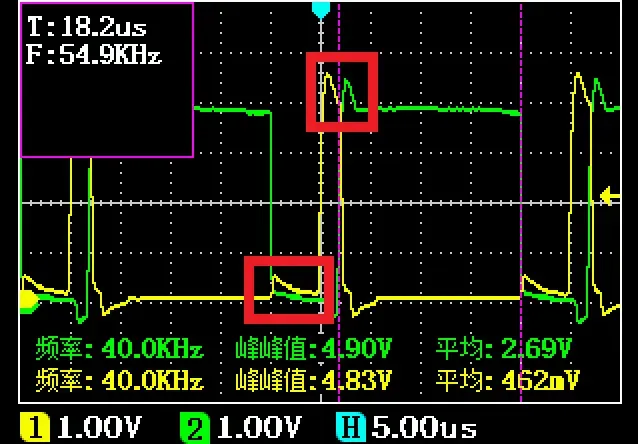

上述测试结果显示电路正常工作,输出电压存在约0.2V-0.3V的固定偏差,这是因为几个采样电阻R2、R7、R8笔者使用了1%精度的基础库电阻进行贴片,实际应当替换为0.1%或更高精度的电阻。栅极波形良好,未观察到明显振铃现象,栅极开通波形凸起峰值高约560mV是三极管的BE结压降(详见第二章)。此外还可以观察到,副开关管关断期间在主开关管关断瞬间出现抬升(见下图)并随着输出功率增大而变得更明显。这其实是漏极寄生电感的感应电压通过MOS管的Cgd寄生电容耦合到了栅极上造成栅极电压抬升,随后再由栅极1K下拉电阻进行泄放。实测该电压最大约为130mV低于AO3400的650mV最小开启电压而不影响正常工作。可以通过减小栅极下拉电阻来减小该异常电压,但代价是增大了栅极驱动损耗。

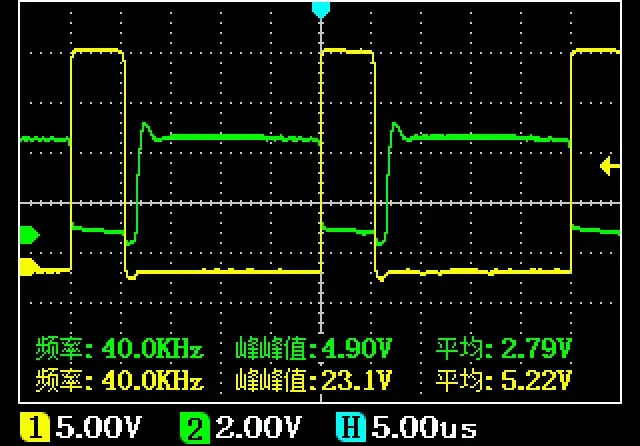

19.9V输出下测试主开关管的栅极(绿色)漏极(黄色)波形如下图所示:

可以看到在栅极电压升高前,漏极电压已略低于0V(体二极管续流)实现软开。测试过程中未发现PCB有任何位置存在明显发热。

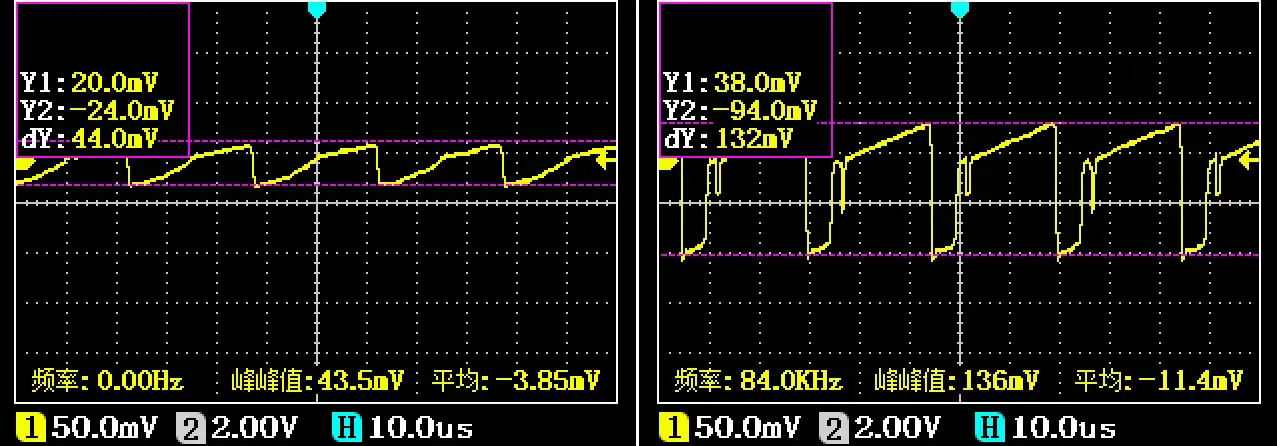

最后分别测试10.1V输出(左图)以及19.9V输出(右图)下的纹波如下图所示:

纹波占比分别约0.44%以及0.66%,可以满足一般使用需求。增大输出电容量、减小输出电容ESR、提高开关频率等有助于改善输出纹波大小。

六、项目总结

本项目主要对ZVT-PWM Boost电路以及栅极驱动电路进行了验证并基于STM32搭建了一个开放的反馈控制算法平台,项目工作原理以及参数计算并不复杂但涉及细节众多包括软硬件、EMC等。项目后续的改进方向可以是:

1、本项目的反馈量采集部分设计考虑不足,采样返回的输出电压电流精度不足且噪声较大对输出稳定性带来了一定影响。软件上可以有针对性地进行滤波降噪处理来改善,但这也不可避免地带来响应延迟进而导致相位裕量不足。硬件上应重点改进电流采样部分,增加有源滤波放大电路改善电流采样质量,同时使用高速比较器和参考电压源等实现硬件级过流过压检测。此外,也可以采集更多的反馈参量供反馈算法设计使用。

2、本项目没有设计上电软启动电路,上电瞬间输入输出电容充电将带来较大的浪涌电流从而有可能触发输入电压源的短路保护。改进措施可以是增加输入端口的软启动电路,有时只需简单串联一枚NTC电阻即可。

3、本项目设定的40KHz驱动频率用于驱动IGBT是合适的但对于AO3400这种MOSFET是偏低的,可以尝试将驱动频率提升至70KHz-90KHz(需重新进行参数计算)这有助于电感电容器件的小型化。

4、本项目设计工作于CCM模式并采用PWM控制适合于重载条件下工作,空载以及轻载情况下将出现“打嗝”现象。改进方案可以是在轻载条件下以DCM方式工作,控制上则可以采用PFM控制。

5、基于串口上位机的交互方式稍显硬核,使用pyQt5等框架可以设计出一款好看易用的操作前端。

设计图

未生成预览图,请在编辑器重新保存一次

未生成预览图,请在编辑器重新保存一次BOM

暂无BOM

暂无BOM 克隆工程

克隆工程工程成员

知识产权声明&复刻说明

本项目为开源硬件项目,其相关的知识产权归创作者所有。创作者在本平台上传该硬件项目仅供平台用户用于学习交流及研究,不包括任何商业性使用,请勿用于商业售卖或其他盈利性的用途;如您认为本项目涉嫌侵犯了您的相关权益,请点击上方“侵权投诉”按钮,我们将按照嘉立创《侵权投诉与申诉规则》进行处理。

请在进行项目复刻时自行验证电路的可行性,并自行辨别该项目是否对您适用。您对复刻项目的任何后果负责,无论何种情况,本平台将不对您在复刻项目时,遇到的任何因开源项目电路设计问题所导致的直接、间接等损害负责。

评论