专业版

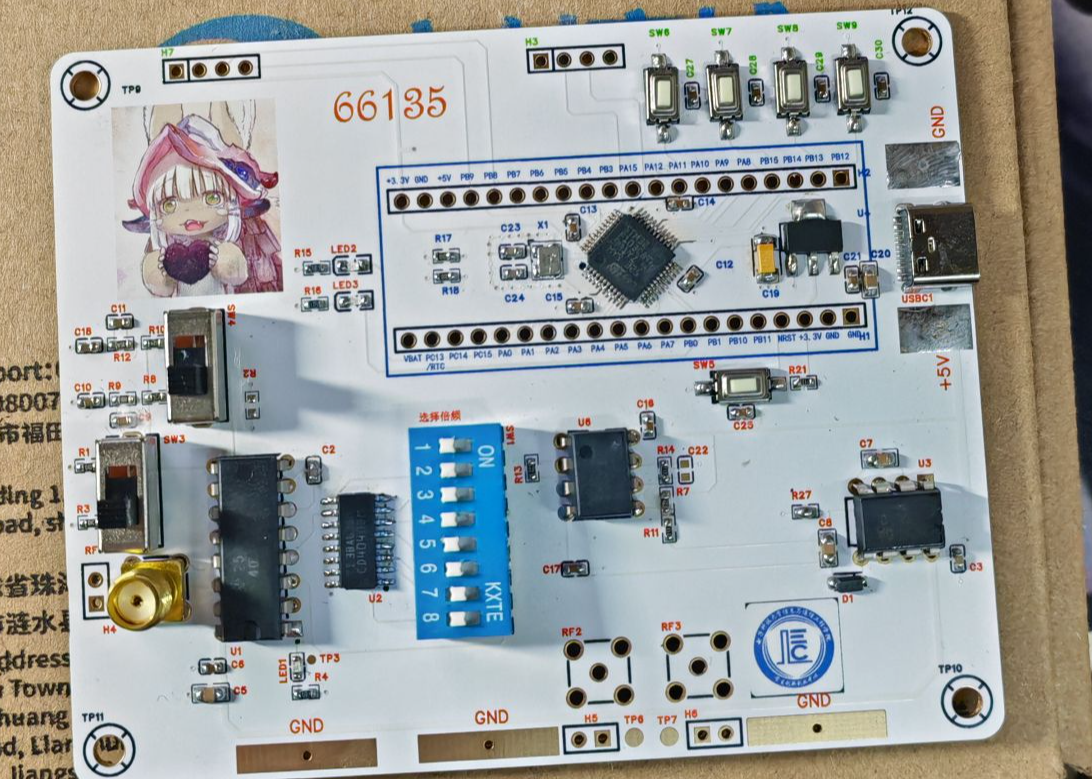

基于CD4046锁相环的倍频电路实现与测试

2.9k

0

0

3

简介

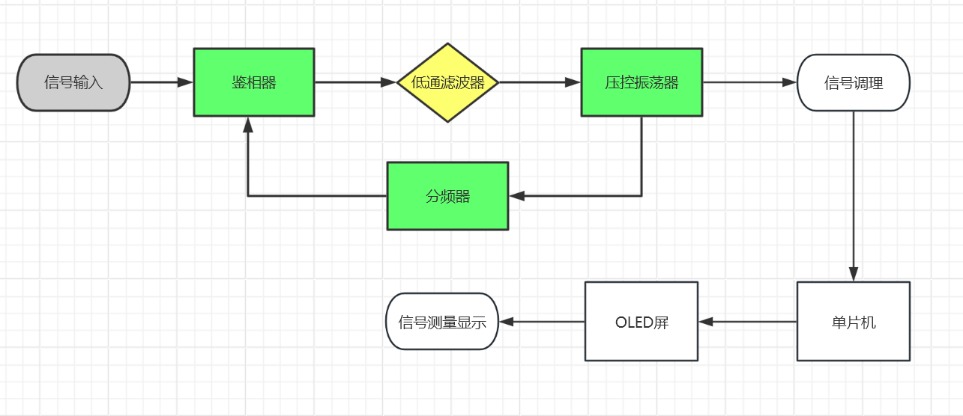

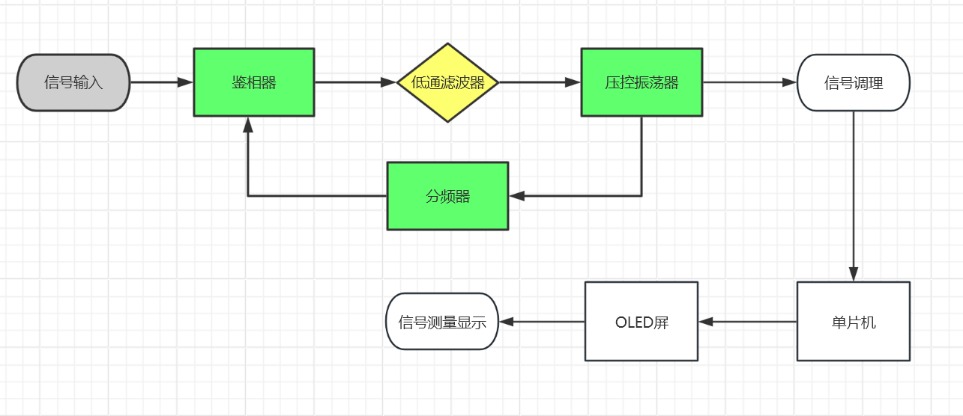

设计基于CD4046芯片的倍频器,并可实现对输出信号进行频率的测量与显示,输入信号fi可由信号源提供,fi的频率范围1KHZ~100kHZ; 实现输出信号频率N倍于输入信号频率(fo=N•fi)

简介:设计基于CD4046芯片的倍频器,并可实现对输出信号进行频率的测量与显示,输入信号fi可由信号源提供,fi的频率范围1KHZ~100kHZ; 实现输出信号频率N倍于输入信号频率(fo=N•fi)开源协议

:CC BY-NC-SA 3.0

(未经作者授权,禁止转载)创建时间:2024-11-06 22:59:52更新时间:2024-12-04 11:20:56

描述

设计基于CD4046芯片的倍频器,并可实现对输出信号进行频率的测量与显示,输入信号fi可由信号源提供,fi的频率范围1KHZ~100kHZ;

实现输出信号频率N倍于输入信号频率(fo=N•fi)

理论分析与计算

1 VCO的配置

依据CD4046的数据手册选择电容电阻确定中心频率

图3:中心频率对应关系

2 环路滤波器设计

利用PLL Design&Simulation进行设计

用扫频的方式测量k0,VCO的输入电压从5V递减到0.3V左右,步长0.1V,记录电压与频率的对应数值,然后通过excel表格做一个线性拟合,得到斜率,然后带入公式反解求出K0。

图4:K0计算

依据要求相位裕度要在50°~ 70°左右,阻尼系数要在0.6~0.8之间,选择合适的截止频率进行仿真,进而得到合适的低通滤波器的电阻电容数据

最后让我们恭喜RA拿下上海mahjor首胜

设计图

未生成预览图,请在编辑器重新保存一次

未生成预览图,请在编辑器重新保存一次BOM

暂无BOM

暂无BOM 克隆工程

克隆工程添加到专辑

0

0

分享

侵权投诉

工程成员

知识产权声明&复刻说明

本项目为开源硬件项目,其相关的知识产权归创作者所有。创作者在本平台上传该硬件项目仅供平台用户用于学习交流及研究,不包括任何商业性使用,请勿用于商业售卖或其他盈利性的用途;如您认为本项目涉嫌侵犯了您的相关权益,请点击上方“侵权投诉”按钮,我们将按照嘉立创《侵权投诉与申诉规则》进行处理。

请在进行项目复刻时自行验证电路的可行性,并自行辨别该项目是否对您适用。您对复刻项目的任何后果负责,无论何种情况,本平台将不对您在复刻项目时,遇到的任何因开源项目电路设计问题所导致的直接、间接等损害负责。

评论