[Altera FPGA] EP4CE10F17C8 开发板

简介

采样Altera的FPGA,外设配有SDRAM、RTC、EEPROM、SPI FLASH、OLED、SD、AD/DA、数码管、按键及LEDs。可作为入门学习用,板子测试通过,例程提供NiosII程序。

简介:采样Altera的FPGA,外设配有SDRAM、RTC、EEPROM、SPI FLASH、OLED、SD、AD/DA、数码管、按键及LEDs。可作为入门学习用,板子测试通过,例程提供NiosII程序。开源协议

:CC BY-NC-SA 4.0

描述

一、简介

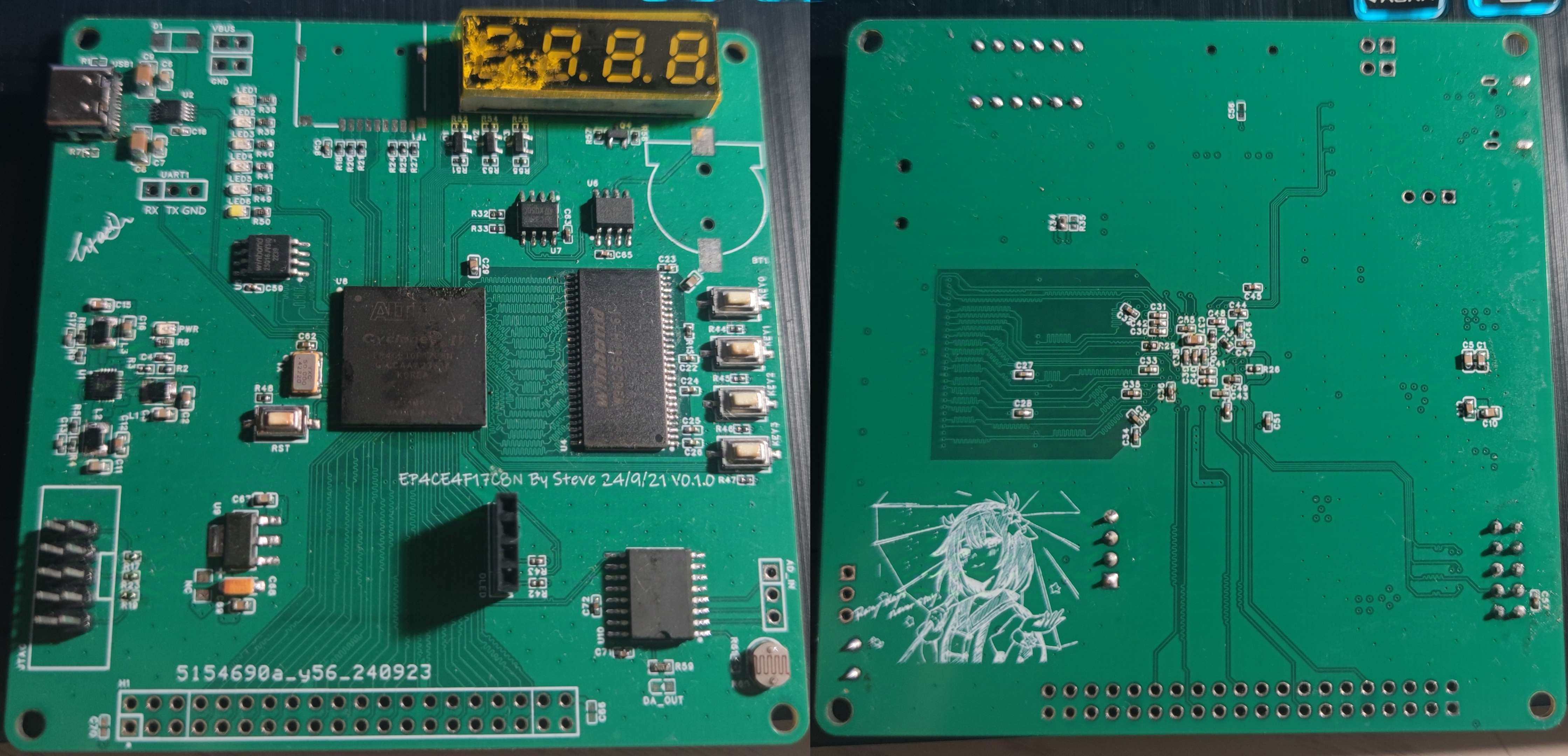

该开发板采用了Altera Cyclone4 EP4CE10F17C8N系列FPGA,配合SDRAM、RTC、EEPROM、SPI FLASH、OLED、SD、AD/DA、数码管、按键及LEDs等外设,方便初学者学习FPGA开发。这个板子主要是我为了应付下课设,之前都用的Xilinx的。

二、硬件

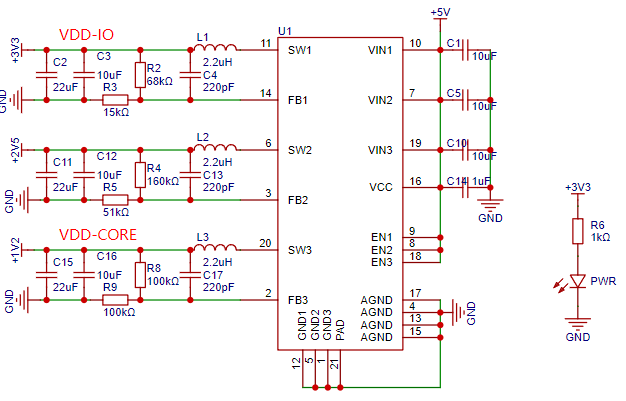

电源部分使用EA3036三路DCDC芯片,并未采样三路LDO的方式,一来减小占用面积二来提高效率也方便简化设计:

由于EA3036总输出功率不超过6W,为了避免外设抢夺电流的情况,单独为外设提供了3.3V的LDO供电。

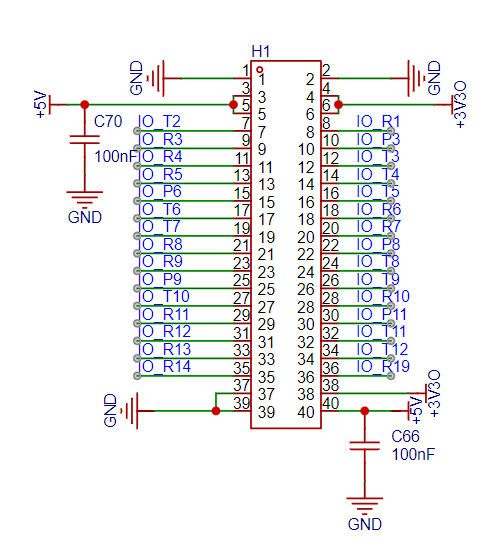

下图是引出的外设结构:

至此,板上外设验证了SDRAM、SPI-Flash、RTC、段码屏、按键、led、oled、uart均正常工作,未做验证的外设:tfcard、eeprom。

fpga核心引脚未全部引出、PCB上留有40pin排针输出:

该40pin兼容兼容正点原子系列开发板,兼容其AD/DA采集模块(未测试)。

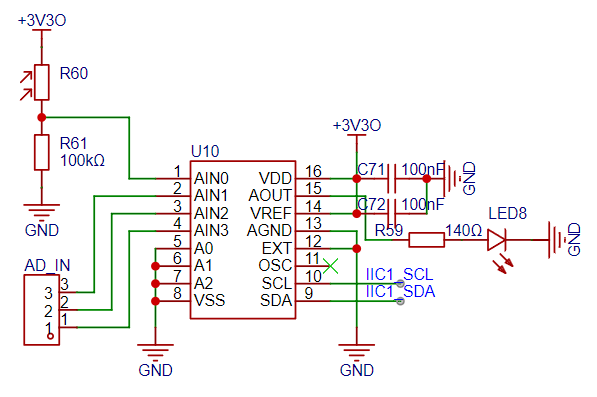

其次,引入了一个较为简单的AD/DA芯片,pcf8591,IIC接口,操作简单方便。

AIN0用于采集光敏电阻分压,其他三输入引出、DAC输出接LED可实现呼吸灯等功能(代码中没有写该功能,但dac操作函数已经留在那儿了)。

其他不必过多说明,参见原理图。

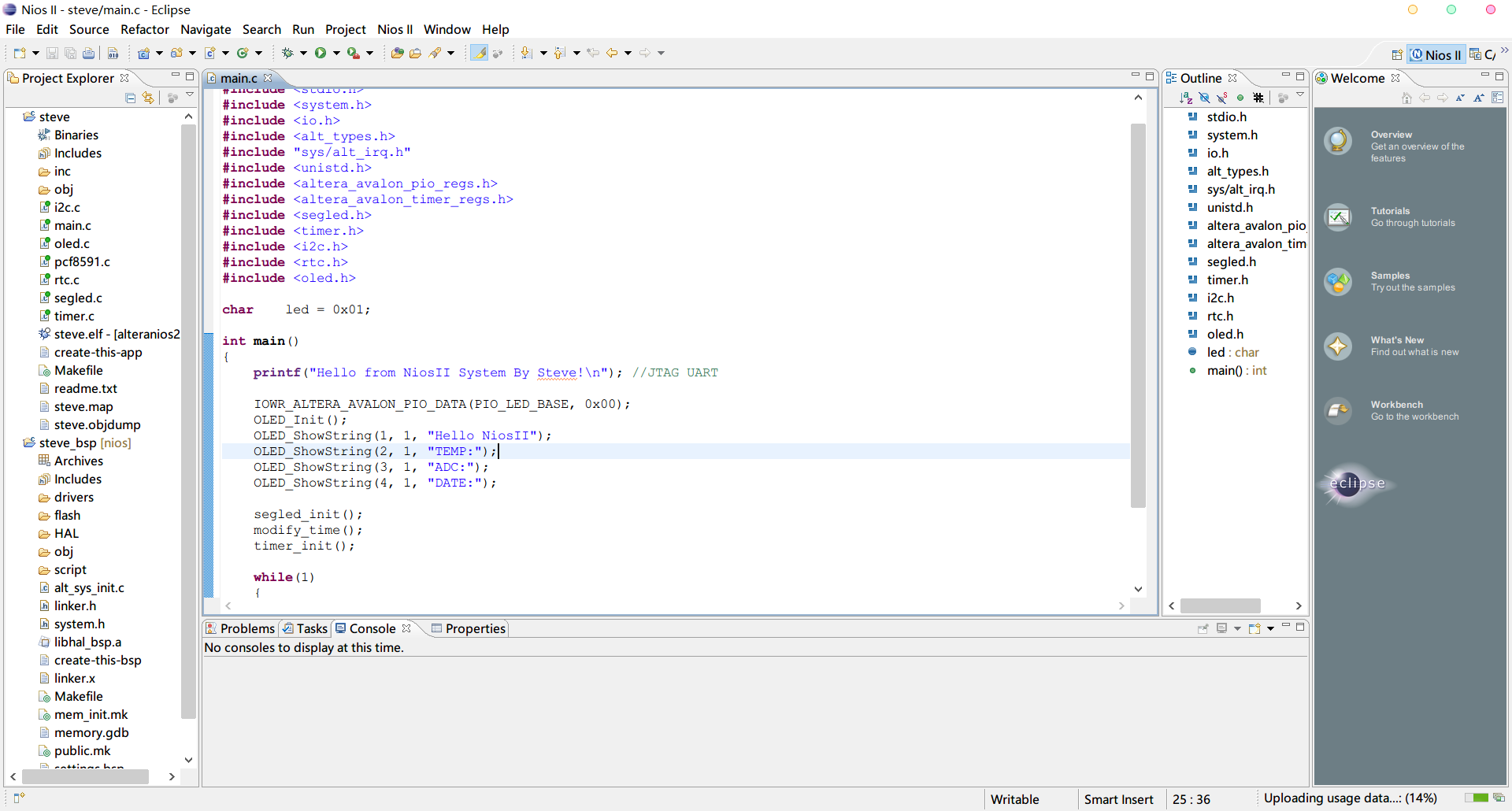

三、提供代码

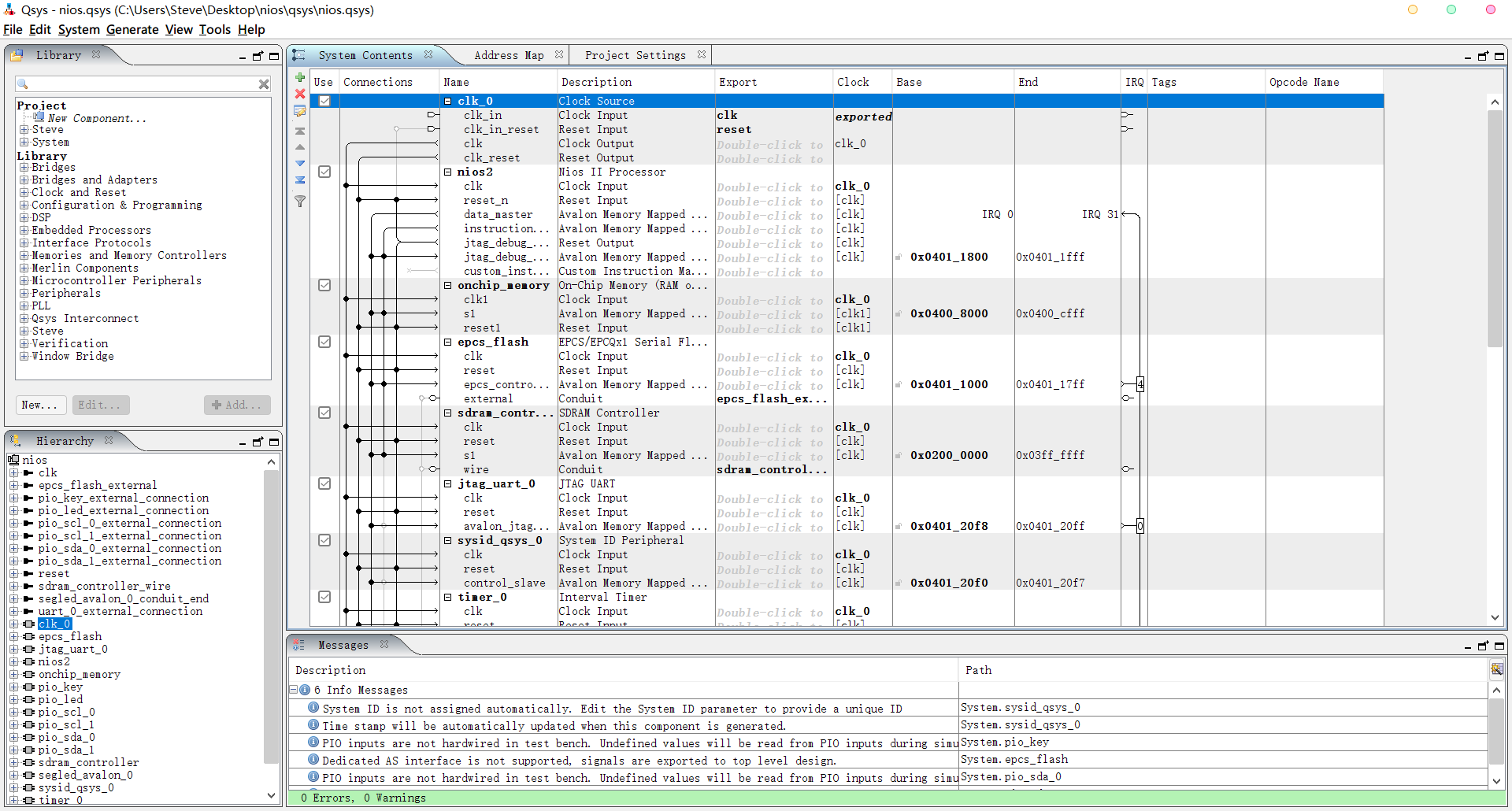

文章提供NiosII软核源码,代码使用在QuartusII13.1.0及QuartusII18.1.0中搭建的NiosII软核,控制段码屏动态刷新显示时间;OLED显示温度、日期、AD采样数据等;控制AD采样光敏电阻数据;控制LED流水的等功能。基本使用了板子上的大部分外设,NiosII的RAM设置为SDRAM,其运行在100MHz下。

上图是qsys中搭建的niosII核,从上到下为:时钟源、nios软核(将reset地址设置到epc、exception地址设置到sdram)、onchipRAM(分配20KB、自行修改或删除)、SDRAM控制器(自行根据芯片修改时序信息)、jtag uart、sysid

、timer定时器、(之后到在图中未展示)一组PIO(key、leds、iic0、iic1)、段码屏驱动自定义IP核。

之后导出生成,写好顶层,分配好管脚即可。需要注意的是,我们要自行分配SDRAM的时钟,相位延迟-75°或其他值,使用PLL实现:

*注:nios的时钟也通过pll的clk c0输出,且不建议添加lock输出和reset输入,我这儿添加后会出现下载验证出错的毛病。

软件也提供了,可以自行参考,IIC驱动移植自正点原子。其他逻辑基本都在定时器中断里。

**关于下载器

PCB引出的JTAG为标准2*5pin JTAG下载口,可兼容大部分usb blaster下载器。本文使用的是淘宝上五六块买的下载器,能用就行没要求,如图(某宝一大堆卖的):

要是有想法的可以把这个集成到板上,可以参考https://x.jlc.com/platform/detail/cd5f440c6fac4317bbec31f5a4b644eb 【本人未验证】

PCB实物:

**附件为QuartusII18.1.0的工程打包文件,请将qar首先解包,并将压缩包中的文件呀复制到工程根目录下(弹出对话框选择替换所有)!!!eclipse定位到根目录software文件夹下。

设计图

未生成预览图,请在编辑器重新保存一次

未生成预览图,请在编辑器重新保存一次BOM

暂无BOM

暂无BOM 克隆工程

克隆工程知识产权声明&复刻说明

本项目为开源硬件项目,其相关的知识产权归创作者所有。创作者在本平台上传该硬件项目仅供平台用户用于学习交流及研究,不包括任何商业性使用,请勿用于商业售卖或其他盈利性的用途;如您认为本项目涉嫌侵犯了您的相关权益,请点击上方“侵权投诉”按钮,我们将按照嘉立创《侵权投诉与申诉规则》进行处理。

请在进行项目复刻时自行验证电路的可行性,并自行辨别该项目是否对您适用。您对复刻项目的任何后果负责,无论何种情况,本平台将不对您在复刻项目时,遇到的任何因开源项目电路设计问题所导致的直接、间接等损害负责。

评论