STM32H723 AD/DA FSMC接口拓展模块

简介

基于STM32H723ZGT6设计的FSMC接口的核心板。适用不熟悉Xilinx ZYNQ 平台,但需要FPGA进行高带宽运算/并行加速的场景。

简介:基于STM32H723ZGT6设计的FSMC接口的核心板。适用不熟悉Xilinx ZYNQ 平台,但需要FPGA进行高带宽运算/并行加速的场景。开源协议

:MIT License

(未经作者授权,禁止转载)描述

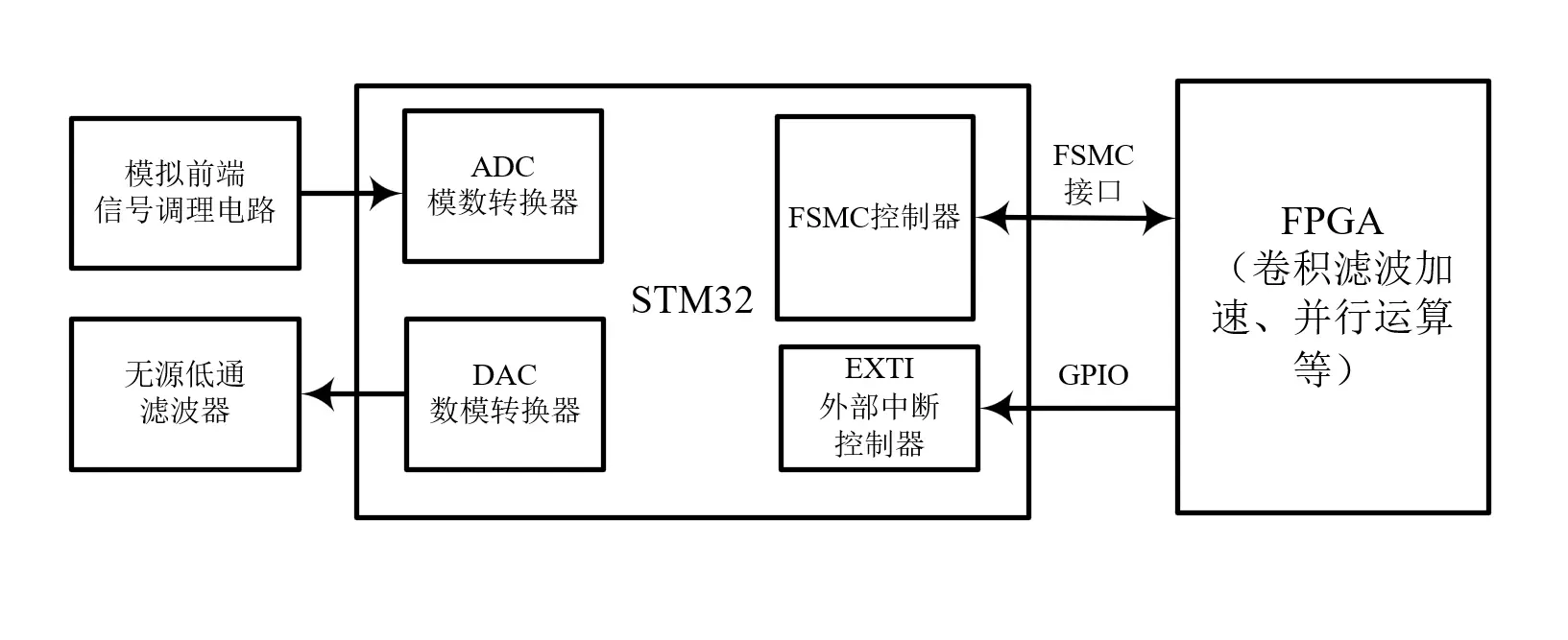

引言:总所周知,STM32是目前电子类专业大学生最熟悉不过的MCU,其开发环境简单,公开教程资料众多,是电子竞赛中使用最多的单片机芯片。目前,STM32H723芯片在淘宝上的售价已降到¥20左右,却拥有550MHz+的主频(实测可超频到660MHz+),外加许多参数非常不错的模拟IP(ADC、DAC、AMP等)。本项目基于STM32H723微控制器芯片,设计一款带有ADC、DAC模拟接口以及FSMC并行接口的模块。

关键词:STM32;FPGA;数字信号处理;高速接口设计;卷积加速;

摘要:本模块基于STM32H723ZGT6,等长引出FSMC接口,引出2通道ADC及2通道DAC(包括ADC前级输入调理电路、DAC输出RC低通滤波网络),可选外部/内部模拟基准电压。适用于使用FPGA做主控的情况下,需要使用ADC、DAC或协处理器的情景。

应用场景及方案:

本模块可应用于STM32进行数据采集,FPGA进行并行数据处理加速(如卷积滤波运算),最后由STM32进行模拟数据输出等场景。相较于STM32与FPGA之间使用SPI等串行协议通信方式,具有访问简单(可直接地址访问)、Verilog设计简单(可映射到FPGA RAM资源)、访问延时低、带宽高 等突出优点;相较于使用ZYNQ SoC,有开发简单、入门门槛低、可移植性强等优点。

本模块引出16根FSMC地址线以及16根FSMC数据线,2根NE片选线,最大可支持2个设备 X 216 X 16bit 的地址空间映射(在不复用地址和数据线的情况下)。使用4层PCB设计,拥有内层完整参考平面,模拟、数字电源及GND隔离,可选外部/内部基准电压,板载ADC前级调理(支持抬升及预增益控制功能,无需外接前级电路,信号可直接输入)。

(Tips: 一般情况下,由于FPGA端存在 已更新共享内存空间的数据需STM32读出 的情况,故需要留出1根高位地址线作为外部中断输入IO,供发送FPGA to STM32 中断请求使用)。

图1 模块原理及应用框图

结语:通过FSMC接口,STM32H723(本模块)为主机,FPGA按照FSMC SRAM接口设计从机接口,可实现FPGA和STM32的直接内存交互访问。

附注:

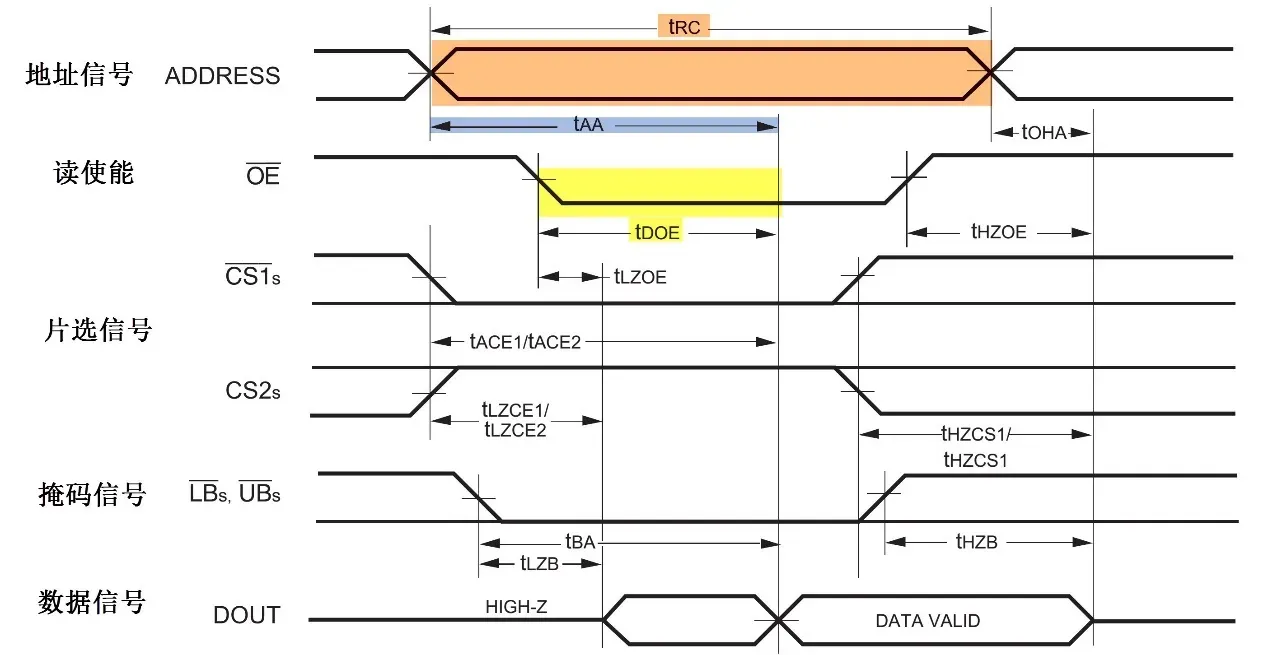

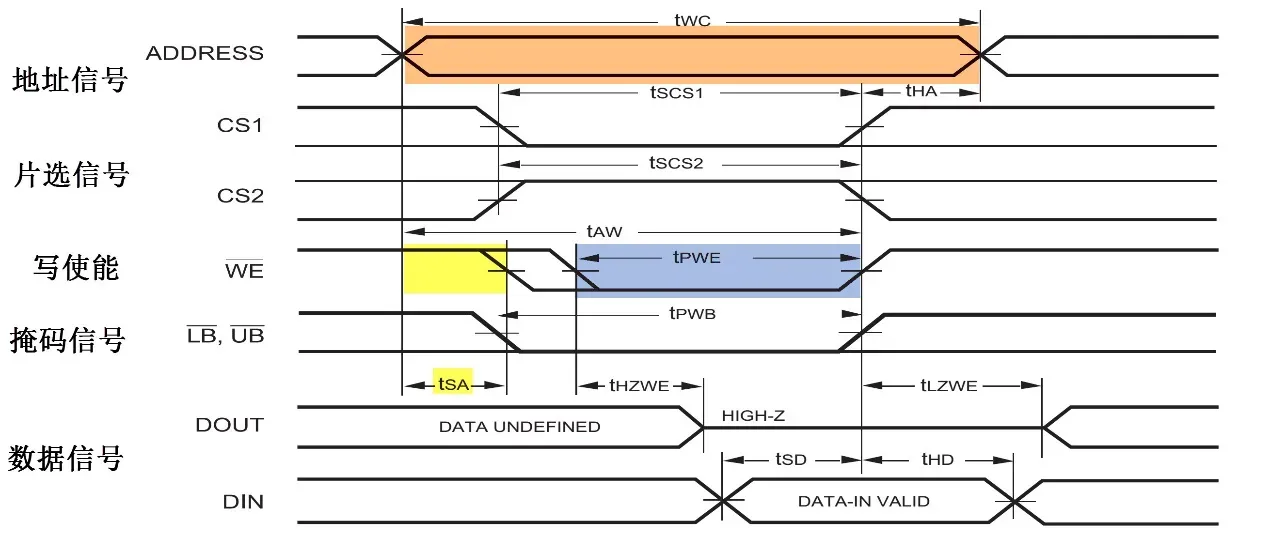

以下是使用FPGA模拟SRAM(Slave),STM32(Host)通过FSMC接口读写的时序参考

图2 FSMC 读时序(FPGA从机模拟SRAM模式)

图3 FSMC 写时序(FPGA从机模拟SRAM模式)

附: systemverilog 从机(伪)代码 (仅供参考)

module fmc_int #( parameter ADDR_WIDTH = xx, parameter DATA_WIDTH = xx) ( //sys_signal input wire rst_n, input wire clk, //fmc interface //fmc选择信号 input wire fmc_ne_i, input wire fmc_noe_i, //0:rd,1:wr input wire fmc_nwe_i, //fmc数据地址线 inout wire [DATA_WIDTH-1:0] fmc_data_io, input wire [ADDR_WIDTH-1:0] fmc_addr_i, input wire fmc_interrupt0_i, //寄存器输出供其他模块使用 output wire [DATA_WIDTH-1:0] reg_out,

...........

) //mem_rd_data:数据读取 reg [DATA_WIDTH-1:0] mem_rd_data; //fmc_wr_en:fmc写入使能信号 wire fmc_wr_en; //fmc_wr_en:fmc读取使能信号 wire fmc_rd_en;

//***************寄存器组*******************//

/* 外部逻辑的读取信号 */ //fmc_wr_en:fmc写入使能信号 assign fmc_wr_en = !fmc_ne_i & !fmc_nwe_i; //fmc_rd_en:fmc读取使能信号 assign fmc_rd_en = !fmc_ne_i & !fmc_noe_i; //fmc_rd_en 电平触发 assign fmc_data_io = fmc_rd_en ? mem_rd_data : {DATA_WIDTH{1'bz}};

//mem_rd_data:数据读取 always_comb begin : FMC_RD_LOGIC case (fmc_addr_i) 'd1: mem_rd_data = reg_out;

.................. default: mem_rd_data = 16'hca_00; endcase end

//wr posedge 写入数据 always @(negedge fmc_wr_en) begin : FMC_WR_LOGIC case (fmc_addr_i)

'd1: mem_rd_data <= reg_out;

.................. default: mem_rd_data <= 16'hca_00;

endcase end

endmodule

本模块40pin接口兼容微相FPGA开发板,可直接连接微相开发板。

(本模块已于2024年打样测试通过,并在2024年电赛作品中应用且获奖)

设计图

未生成预览图,请在编辑器重新保存一次

未生成预览图,请在编辑器重新保存一次BOM

暂无BOM

暂无BOM 克隆工程

克隆工程工程成员

知识产权声明&复刻说明

本项目为开源硬件项目,其相关的知识产权归创作者所有。创作者在本平台上传该硬件项目仅供平台用户用于学习交流及研究,不包括任何商业性使用,请勿用于商业售卖或其他盈利性的用途;如您认为本项目涉嫌侵犯了您的相关权益,请点击上方“侵权投诉”按钮,我们将按照嘉立创《侵权投诉与申诉规则》进行处理。

请在进行项目复刻时自行验证电路的可行性,并自行辨别该项目是否对您适用。您对复刻项目的任何后果负责,无论何种情况,本平台将不对您在复刻项目时,遇到的任何因开源项目电路设计问题所导致的直接、间接等损害负责。

评论