基于EPM240的FPGA/CPLD学习板

简介

想学verilog hdl,但是市面上的FPGA开发板太贵了! >w< 于是自己画了一个。

简介: 想学verilog hdl,但是市面上的FPGA开发板太贵了! >w< 于是自己画了一个。开源协议

:CERN Open Hardware License

描述

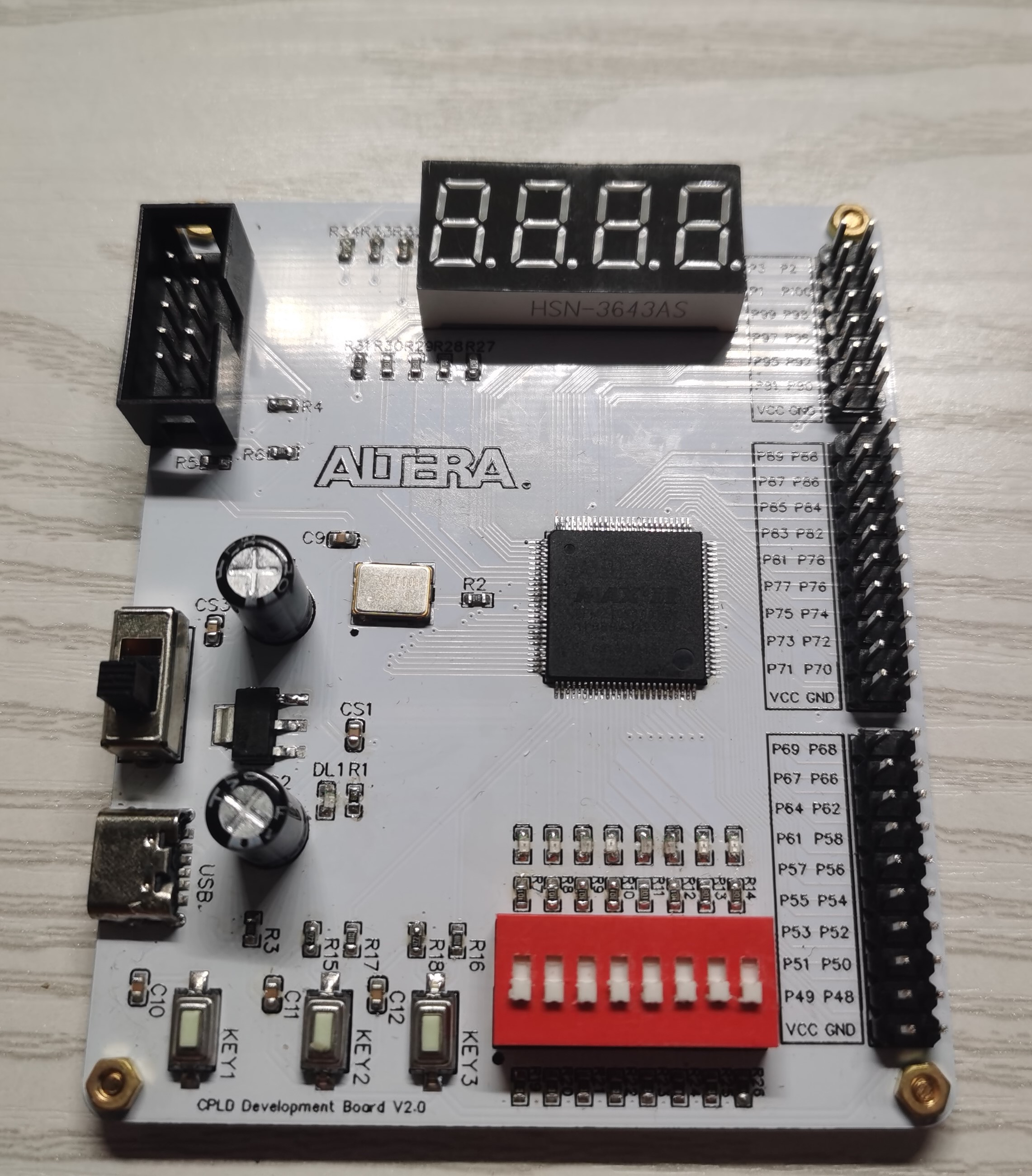

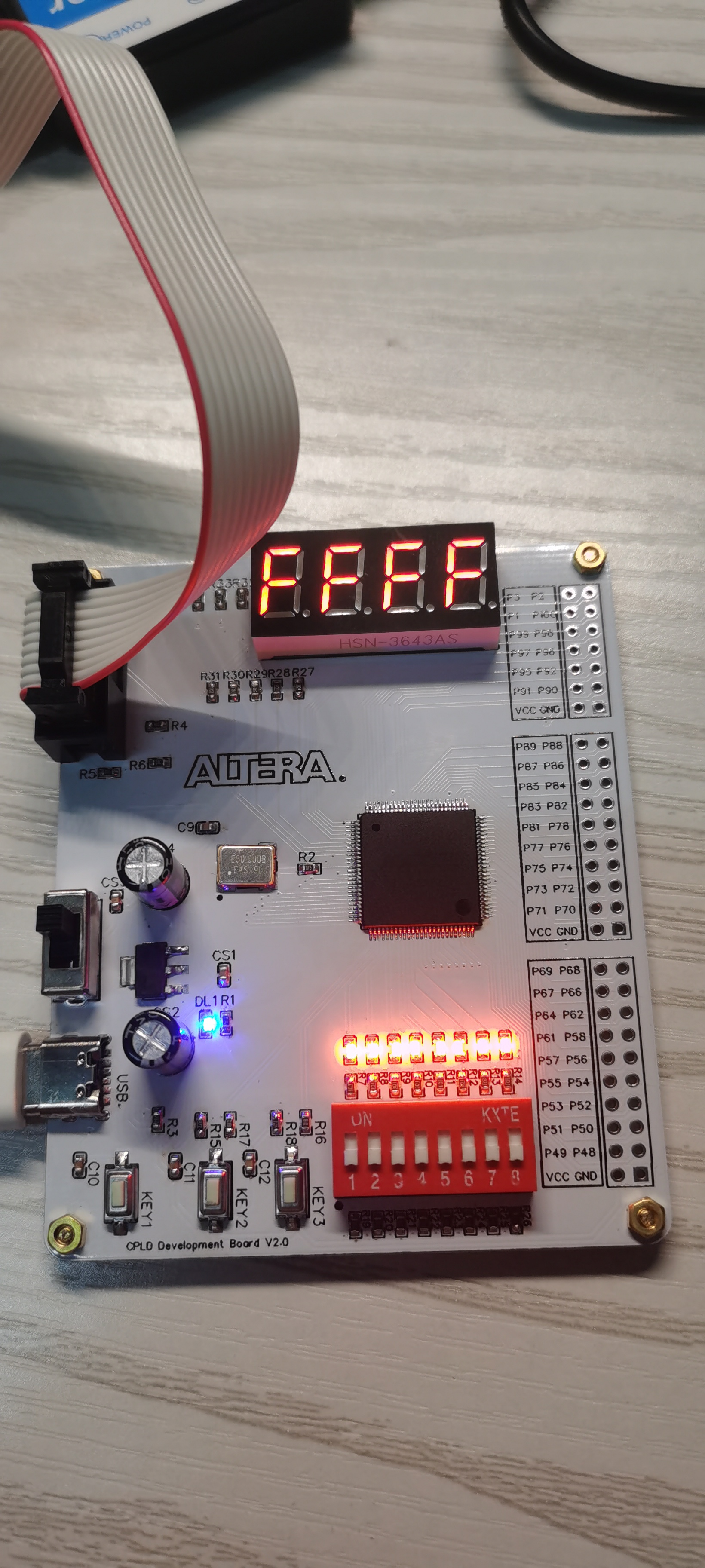

基于EPM240的FPGA/CPLD学习板

想学verilog hdl,但是市面上的FPGA开发板太贵了! >w< 于是自己画了一个。主控成本只要10块,自己有些元器件的话成本很低。适合用来学Verilog语言时做一些小逻辑的验证实验。大家可以参考参考。希望有所帮助!

说明:

主控用的是inter Altera的epm240t100c5n,它属于cpld,与fpga名字不同,但是开发方式差不多。不过相比与fpga它无需进行程序固化操作更加方便。

总体设计方案框图:

软件说明

软件使用quartus,推荐版本为quartus13.1,因为它综合更快嘿嘿。

引脚分配:见附件。

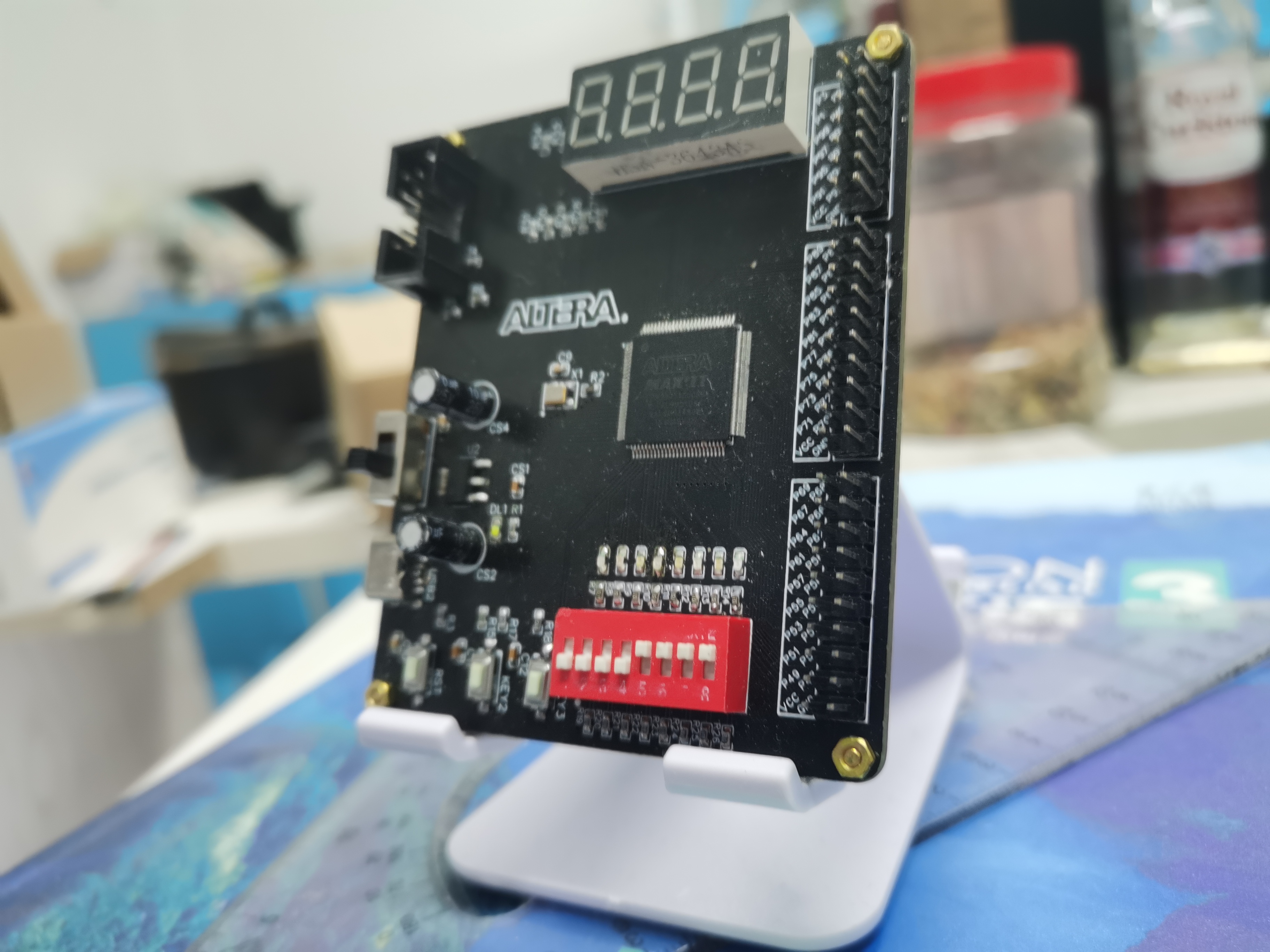

实物展示

吃灰方式:

1、找个手机支架摆上。

2、放在灰尘多的地方。

3、定期拿来吹一吹。

注意事项

1、epm240的引脚无编程时是默认接地的,这会导致led灯莫名其妙亮起来的情况,更改方式为:

第一步:打开Assignment,选择Device。

第二步:出现如图所示的Device面板后选择“Devie and Pin Options...“按钮。

第二步:出现如图所示的Device面板后选择“Devie and Pin Options...“按钮。

第三步:进入后选择”Unused Pins“->选择”As input tri-stated“ok即可。

第三步:进入后选择”Unused Pins“->选择”As input tri-stated“ok即可。

记得每个工程都要如此设置哦~

记得每个工程都要如此设置哦~

2、led灯是负逻辑点亮的,亮灯代表0,写逻辑时可以加反相器改一下。

演示视频

无

其它附件上传

设计图

未生成预览图,请在编辑器重新保存一次

未生成预览图,请在编辑器重新保存一次BOM

暂无BOM

暂无BOM 克隆工程

克隆工程工程成员

知识产权声明&复刻说明

本项目为开源硬件项目,其相关的知识产权归创作者所有。创作者在本平台上传该硬件项目仅供平台用户用于学习交流及研究,不包括任何商业性使用,请勿用于商业售卖或其他盈利性的用途;如您认为本项目涉嫌侵犯了您的相关权益,请点击上方“侵权投诉”按钮,我们将按照嘉立创《侵权投诉与申诉规则》进行处理。

请在进行项目复刻时自行验证电路的可行性,并自行辨别该项目是否对您适用。您对复刻项目的任何后果负责,无论何种情况,本平台将不对您在复刻项目时,遇到的任何因开源项目电路设计问题所导致的直接、间接等损害负责。

评论