USB3.1拓展坞(带读卡器)—— VL822+GL3224

简介

基于VL822设计的拓展坞,带有3个USB3.2的USB口和SD/TF卡插槽

简介:基于VL822设计的拓展坞,带有3个USB3.2的USB口和SD/TF卡插槽开源协议

:GPL 3.0

描述

本工程为AD导入嘉立创改编而来,所以不能使用嘉立创免费打样,在嘉立创下单4层板要60元左右

本工程使用VL822芯片结合GL3224读卡器芯片制作而成的拓展坞,最高支持USB3.1 gen2的速度(1000MB/S)

之前还设计了一些其他的集线器和拓展坞:

USB3.1 gen2 4口集线器(拓展坞)——VL822 - 立创开源硬件平台

USB3.1 gen1集线器(拓展坞)——GL3510 - 立创开源硬件平台

USB3.0拓展坞(带读卡器)——GL3510+GL3224 - 立创开源硬件平台

USB2.0 7口集线器——FE2.1 - 立创开源硬件平台

USBHub2.0(4口)——CH334F - 立创开源硬件平台

目录:

一、电源部分

二、电源电路测试

三、拓展坞速度测试

四、阻抗匹配设置

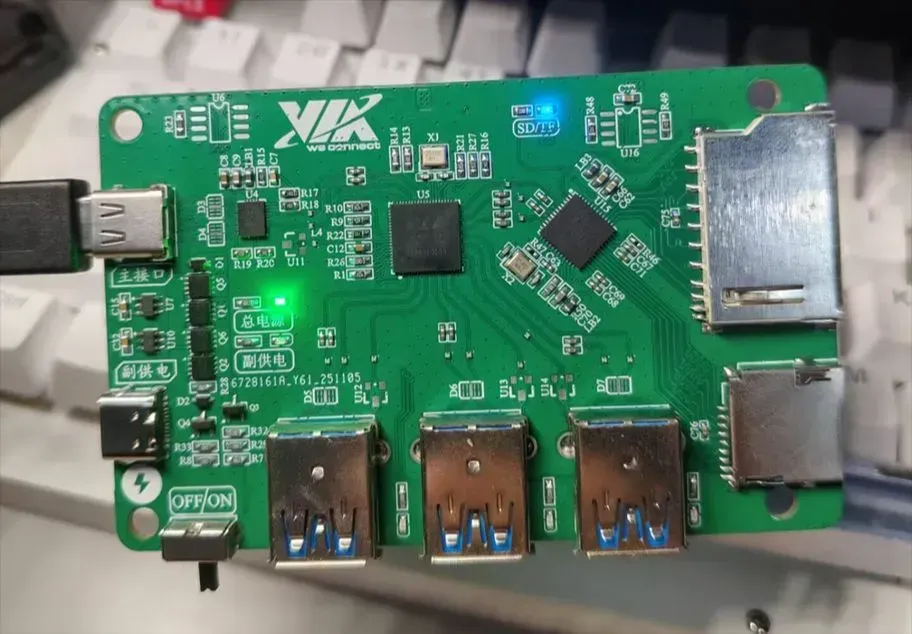

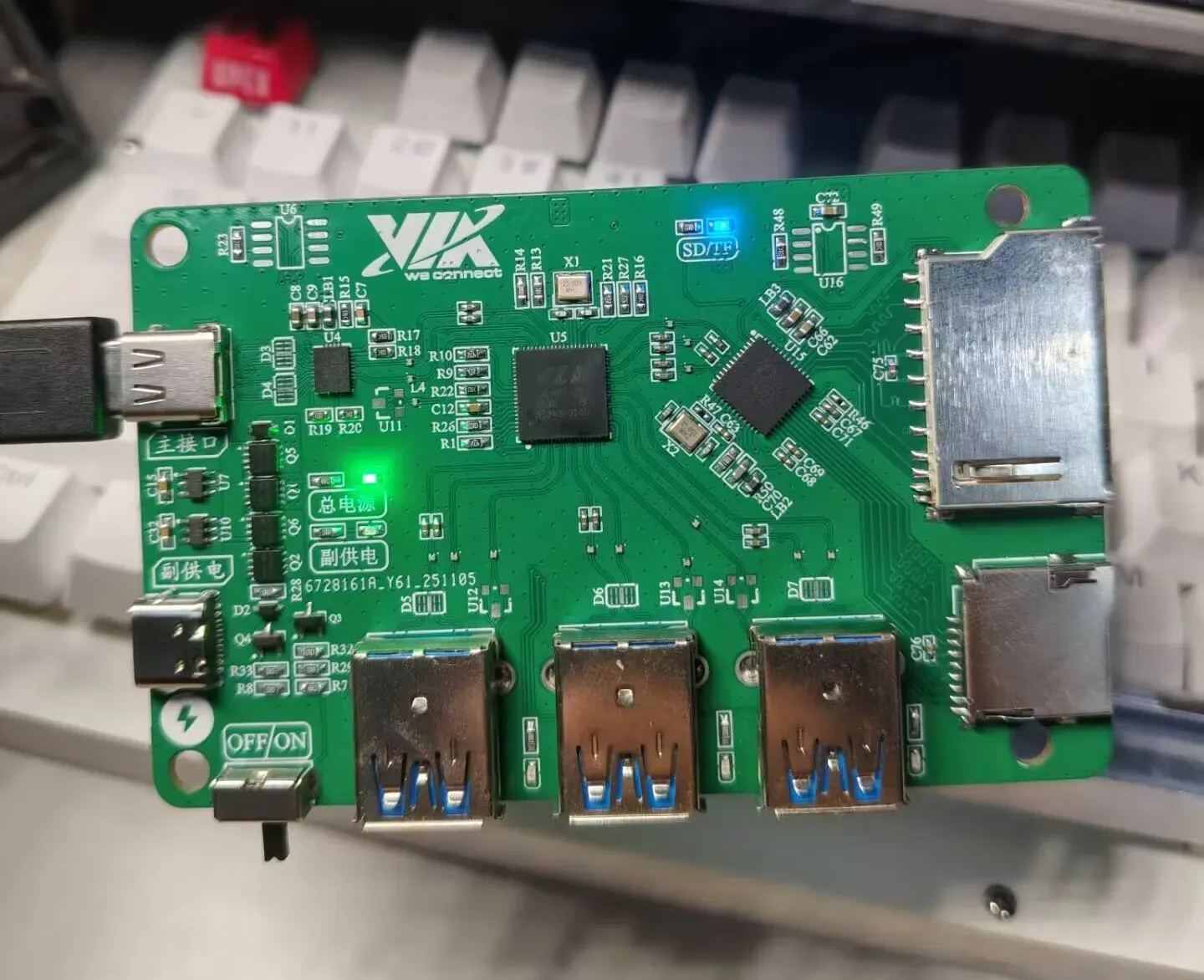

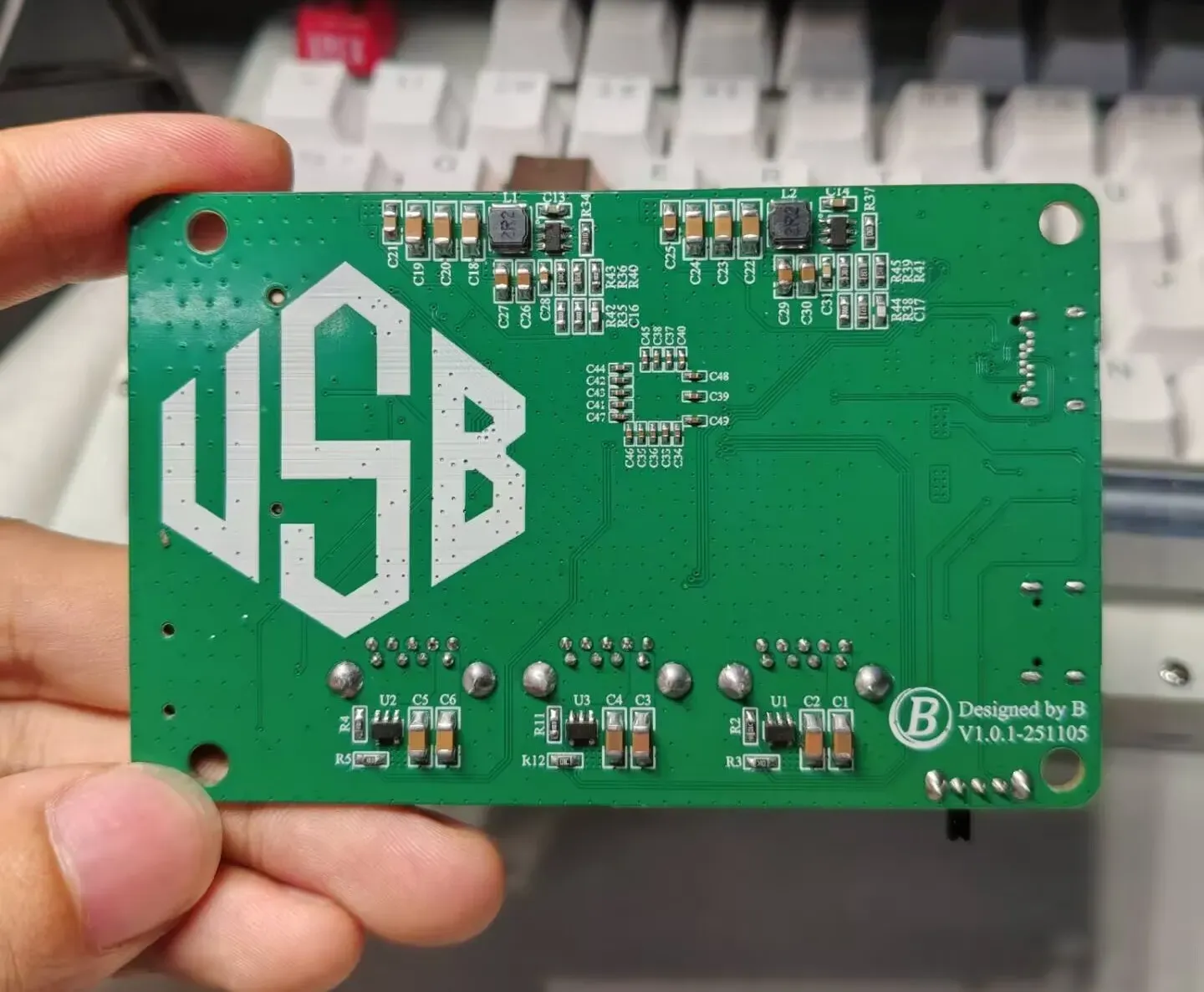

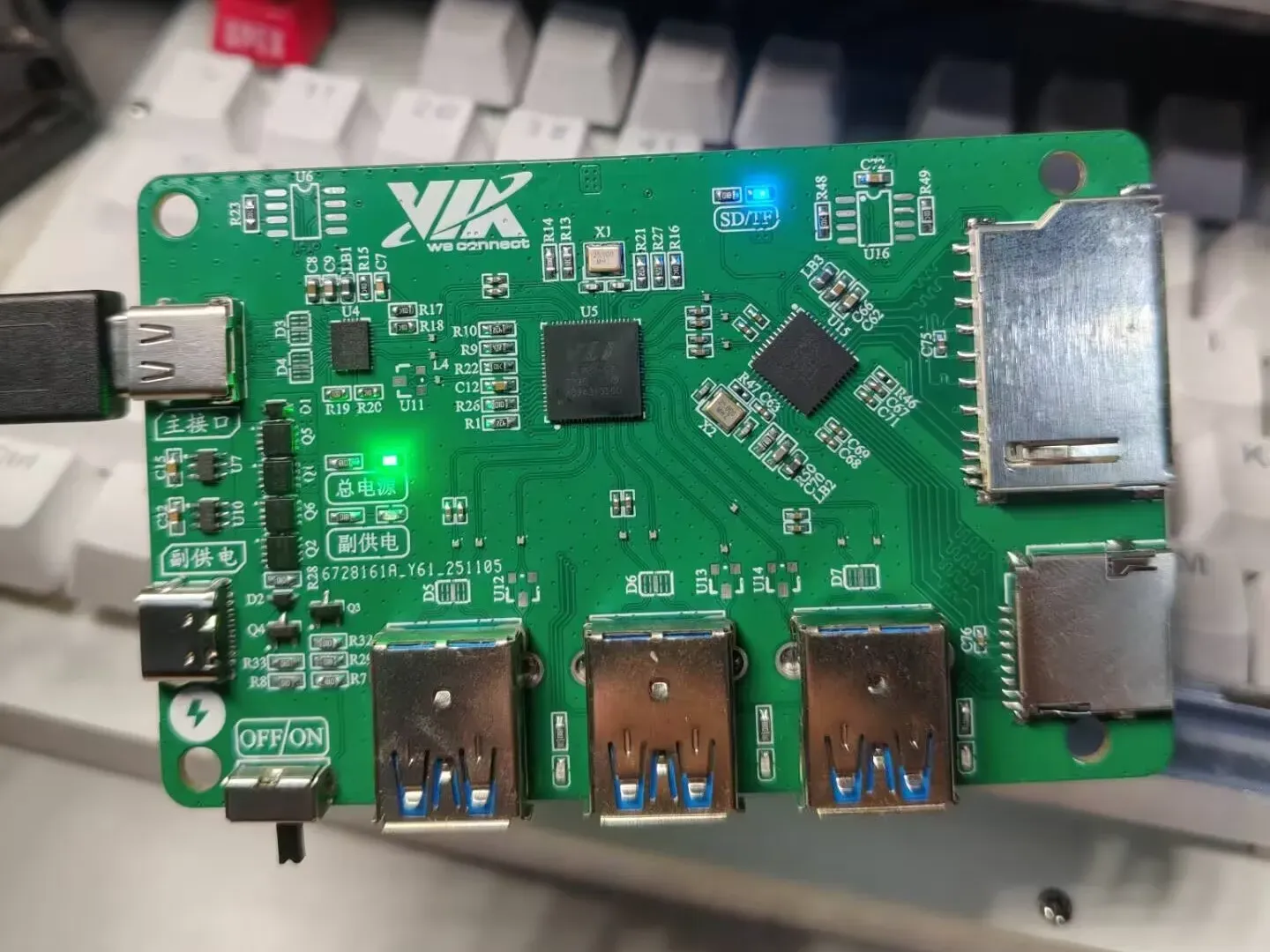

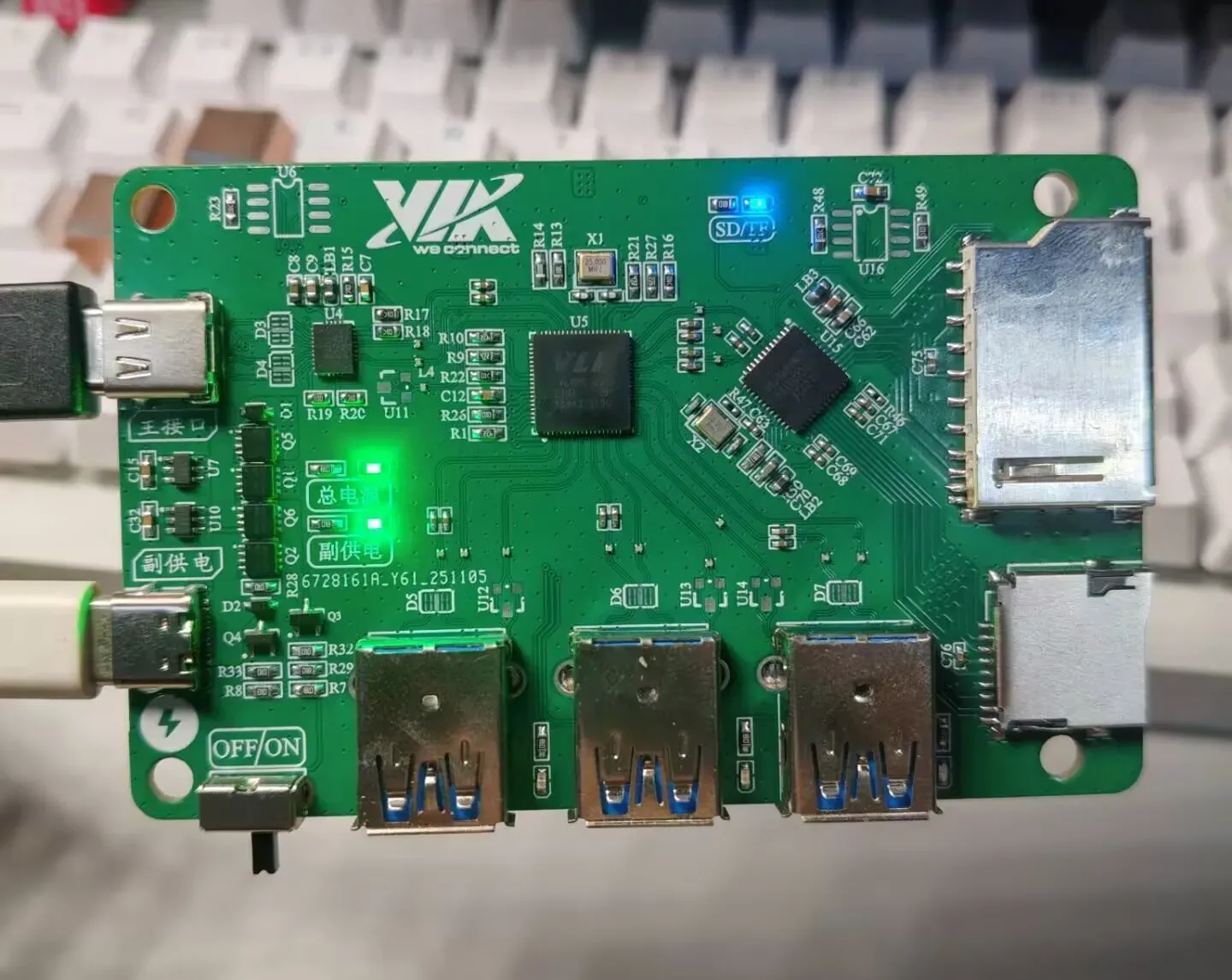

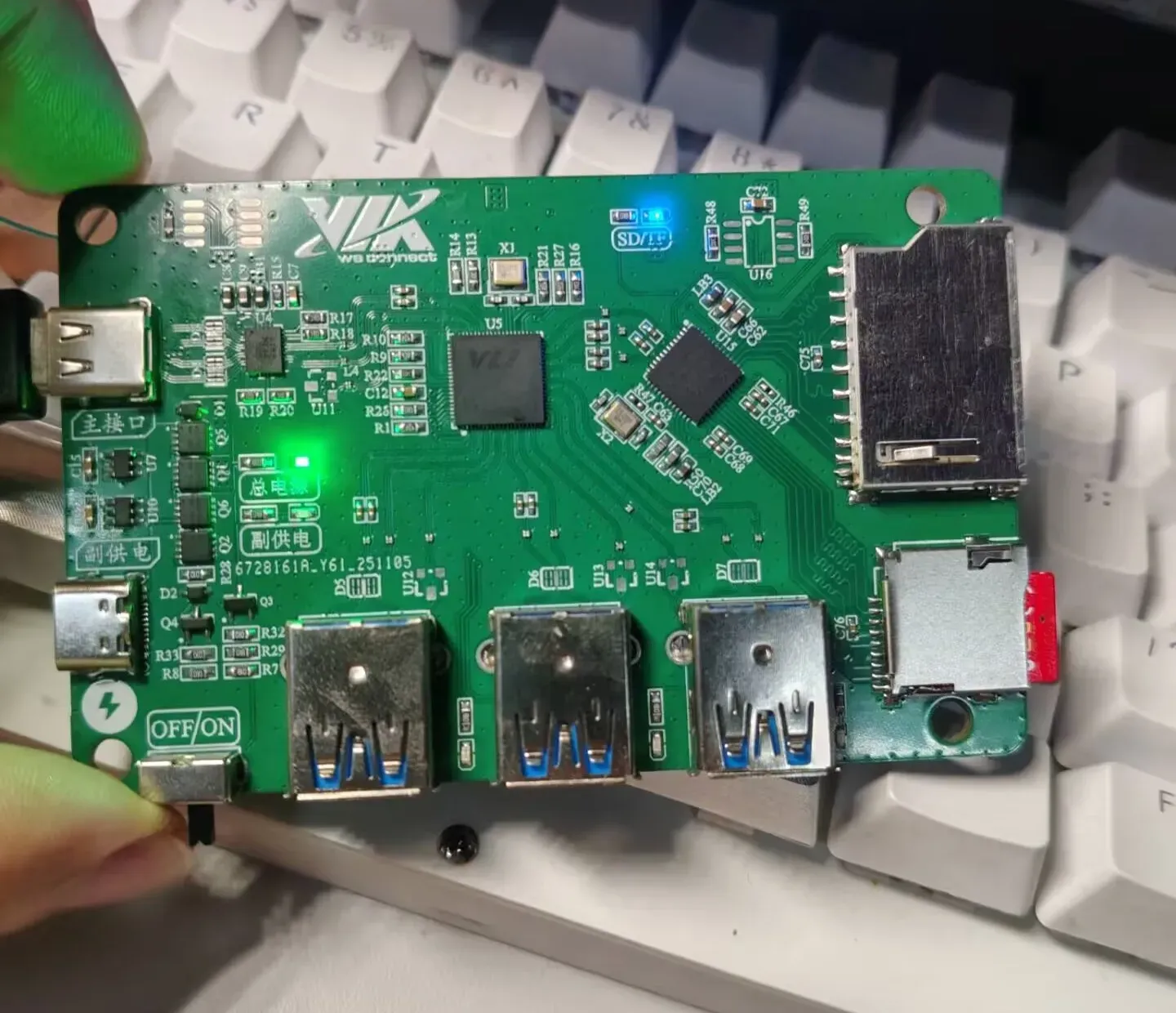

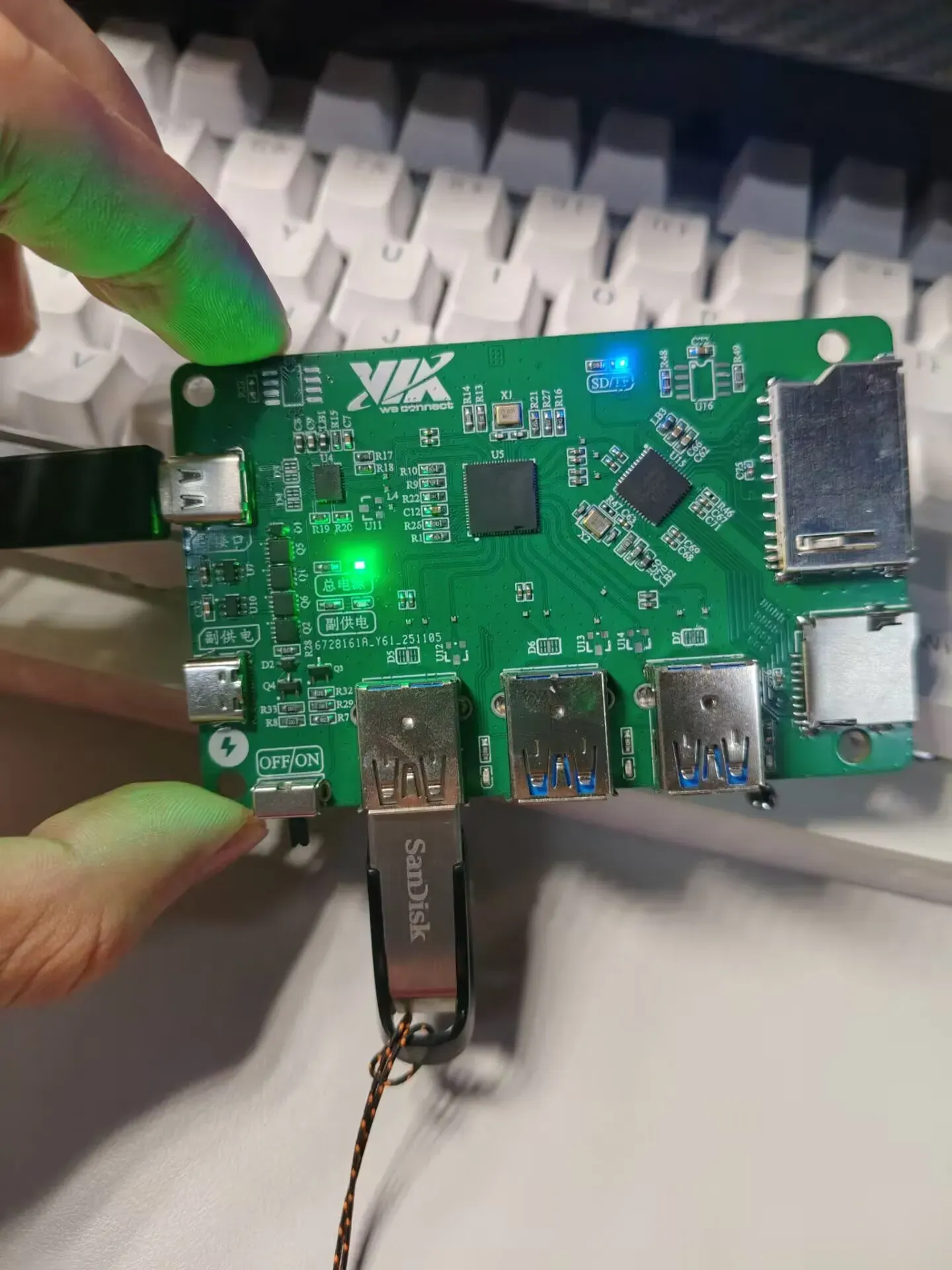

实物图片:

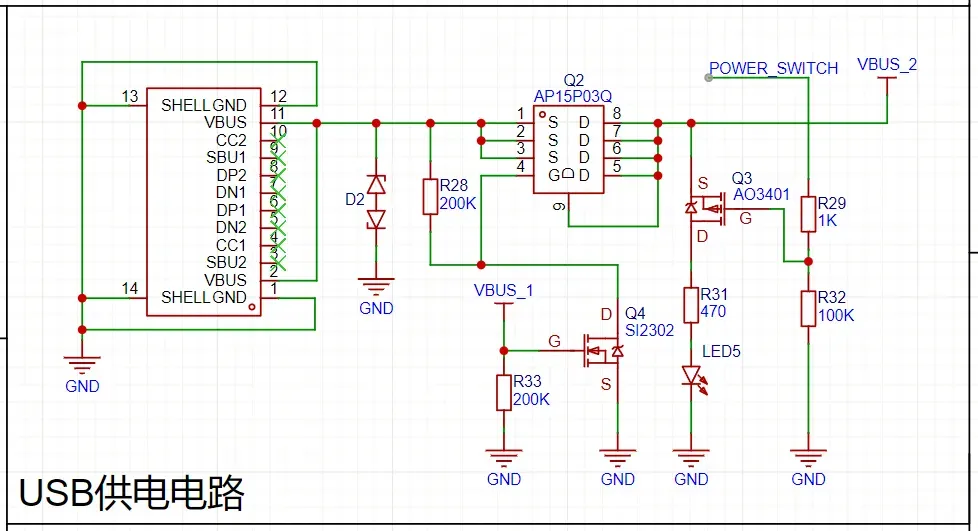

一、电源部分

该部分为该工程设计的亮点:只有主接口接入后通电后,电路的电源才导通(即使副供电接入了电路也不导通)

副供电使用了一个PMOS来控制导通,只有主接口接入时,Q4导通将Q2的栅极拉低,使Q2导通使副供电导通

副供电的指示灯也使用了一个PMOS来控制导通,只有开关导通(接地)时LED5亮起

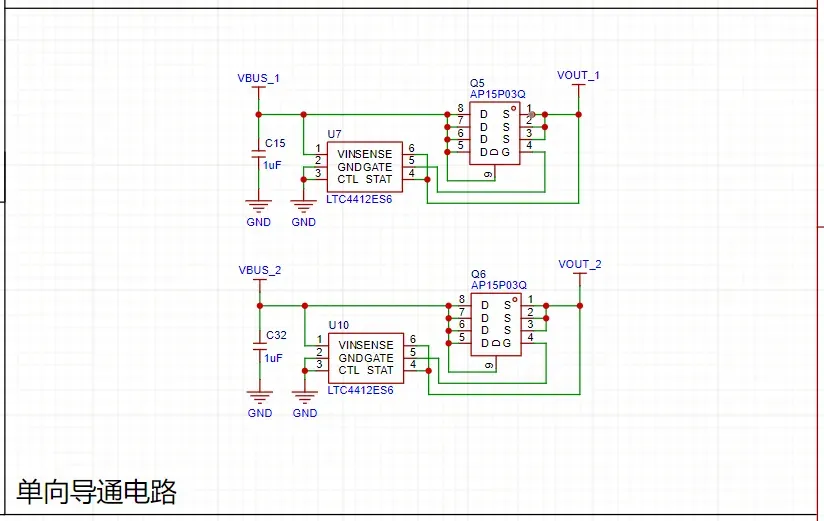

电源的部分使用了LTC4412芯片与外接的一个PMOS组成一个理想二极管电路,使得主电源与副供电之间的电源不会互相干扰

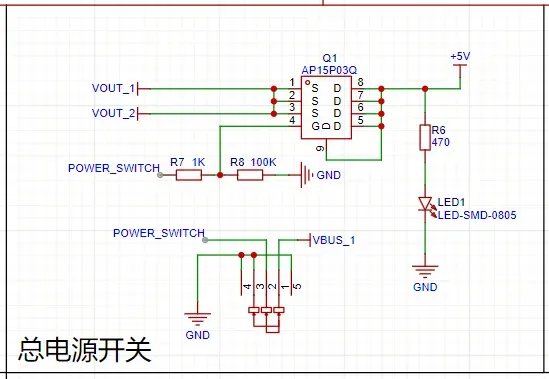

总开关使用了一个PMOS来控制,当开关接地时导通,开关拉高时Q1截止

二、电源电路测试

(1)只有主接口插入时

此时主电源指示灯亮起(PWR),且此时GL3224读卡器控制芯片亮起

(2)当主接口和副供电接口都接入时

可以看到主电源指示灯(PWR)和副供电指示灯(PWR_1)都亮起

(3)当只有副供电接入时

可以看到拓展坞的电源不导通(只有主接口接入且通电后,副供电才会导通)

三、拓展坞速度测试

前提说明:

1、使用的线材最高速度为20Gbp/s(2000MB/s)

2、使用的集线器芯片为VL822最高速度为1000MB/s,使用的读卡器芯片GL3224最高速度为500MB/s

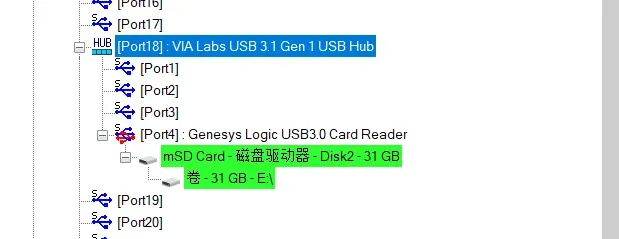

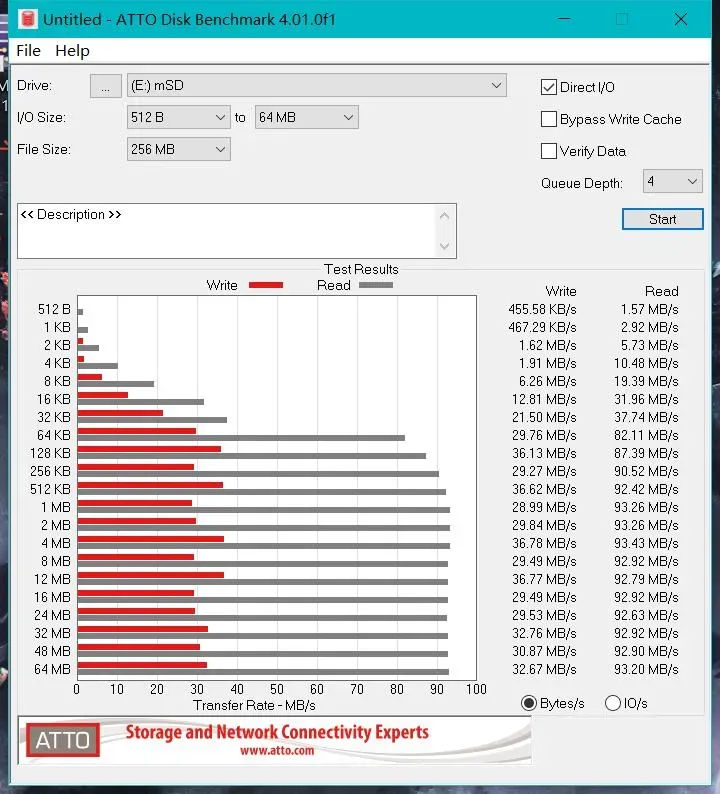

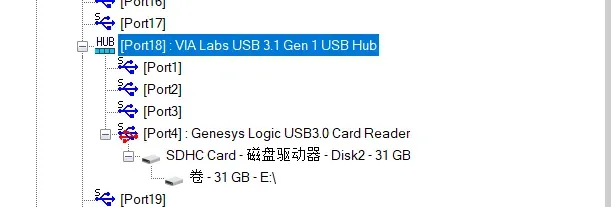

(1)TF卡速度测试

最高速度在92MB/S左右,接近标注的100MB/S,速度还是很不错的

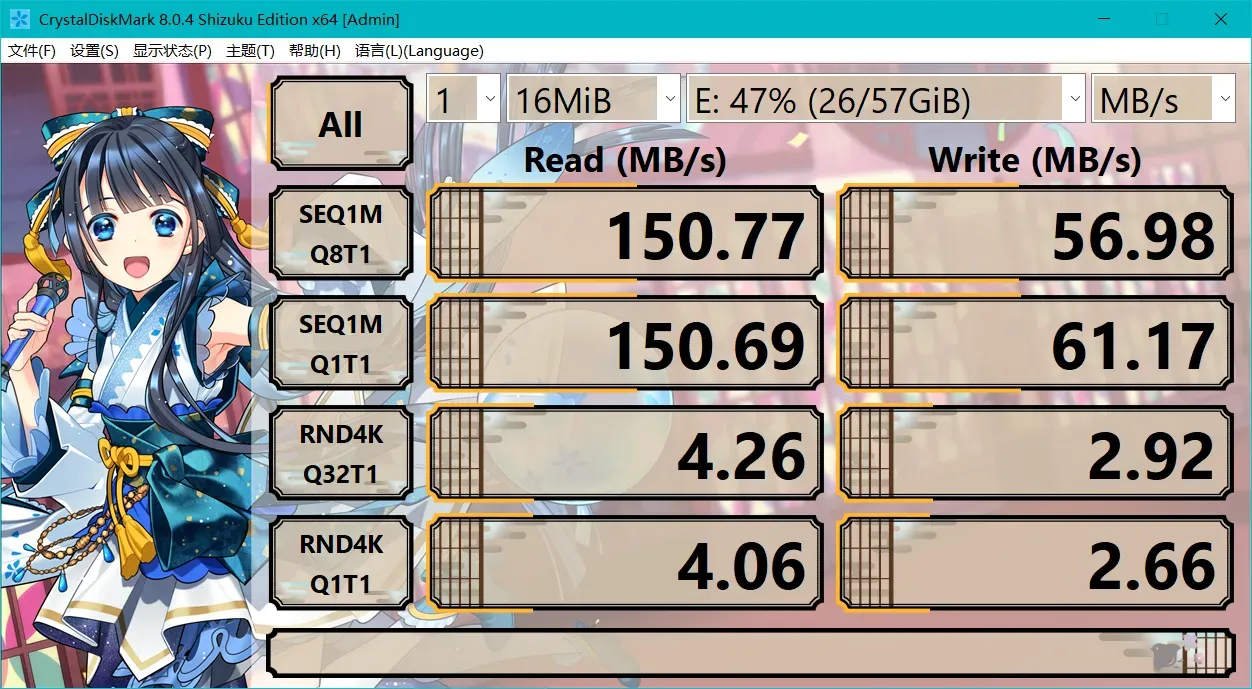

(2)SD卡速度测试

最高速度在92MB/S左右,还是不错的

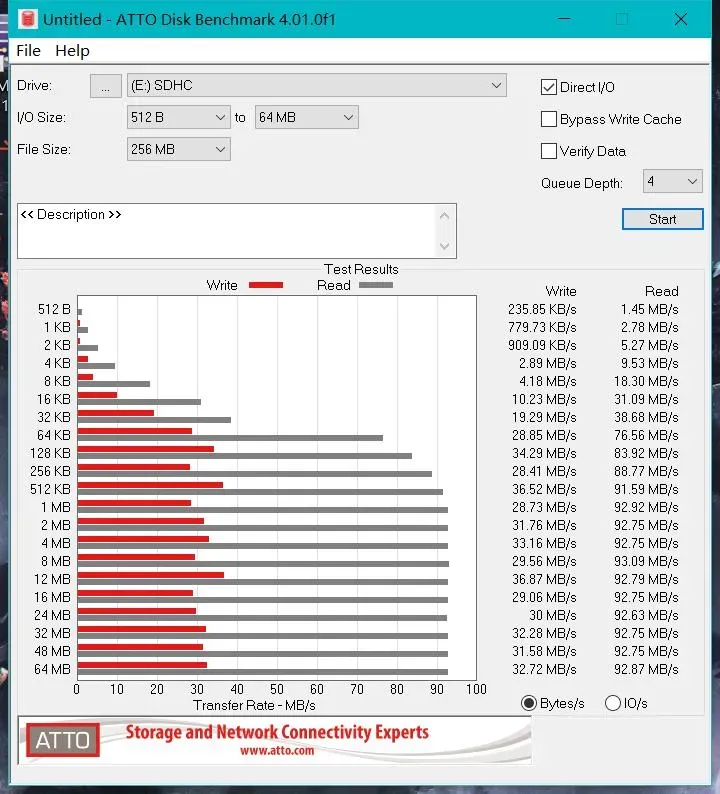

(3)USB口测试

使用的是USB3.0U盘测试的

USB1速度:

USB2速度:

USB3速度:

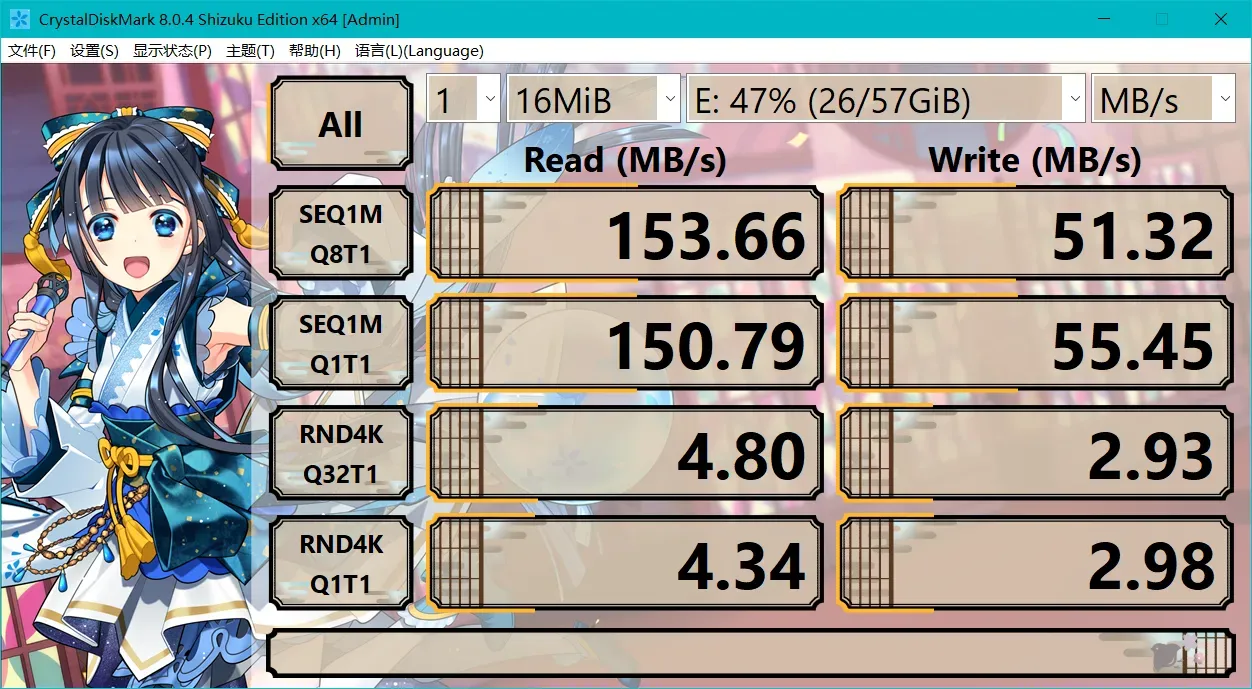

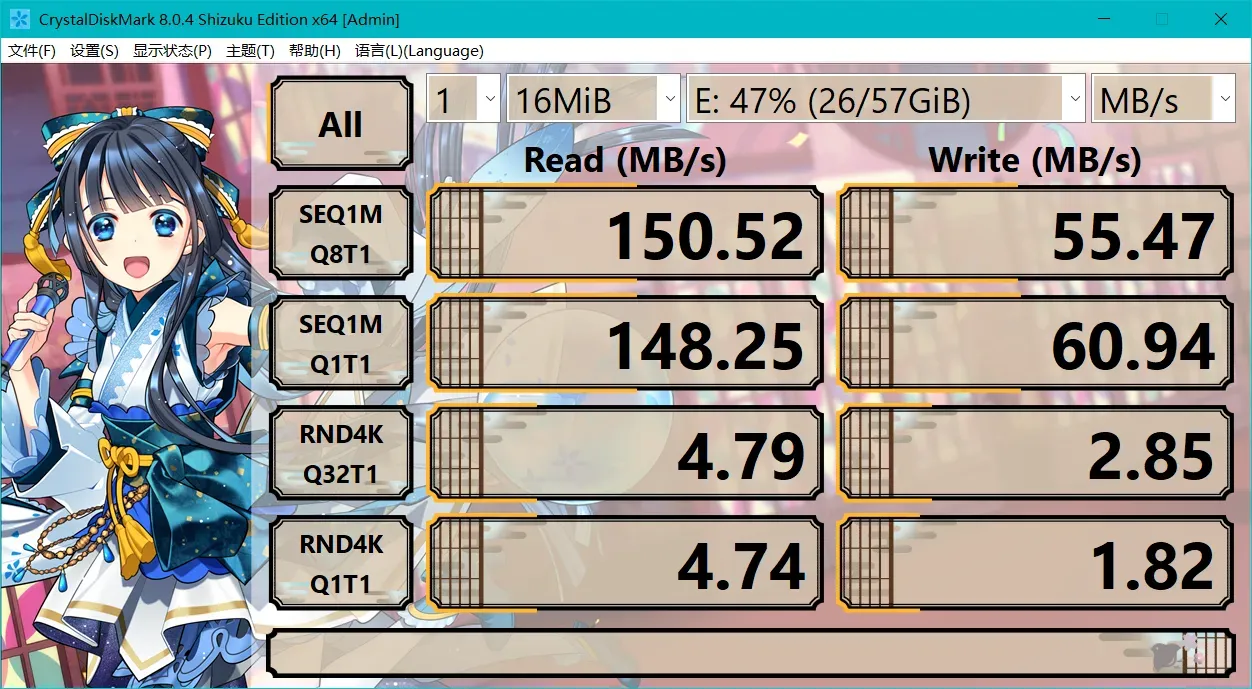

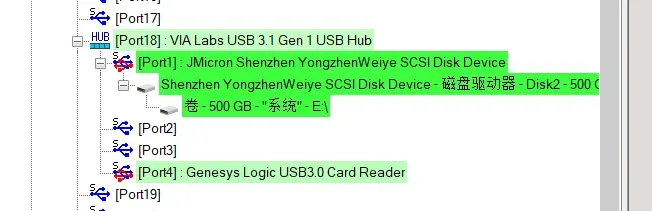

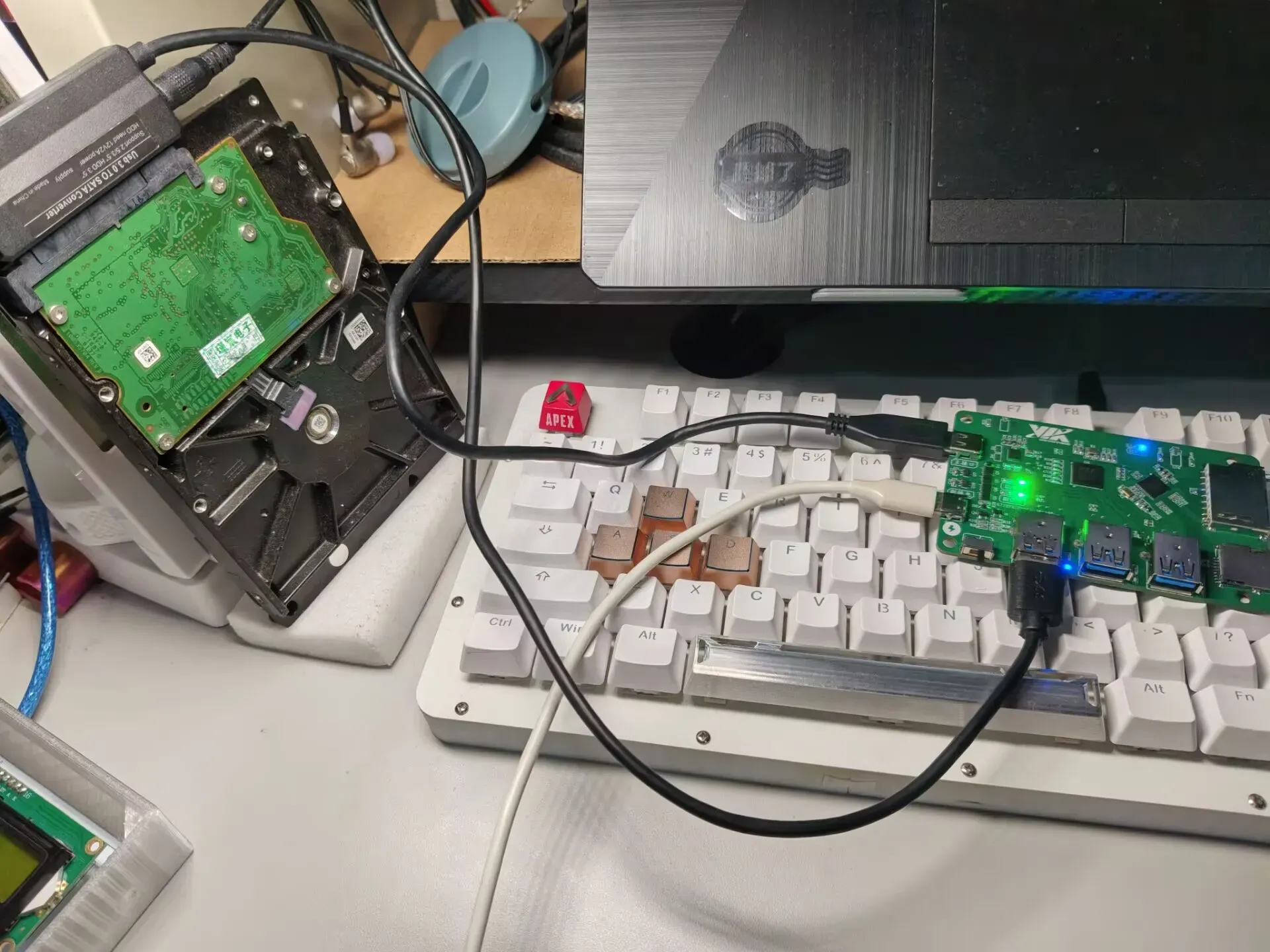

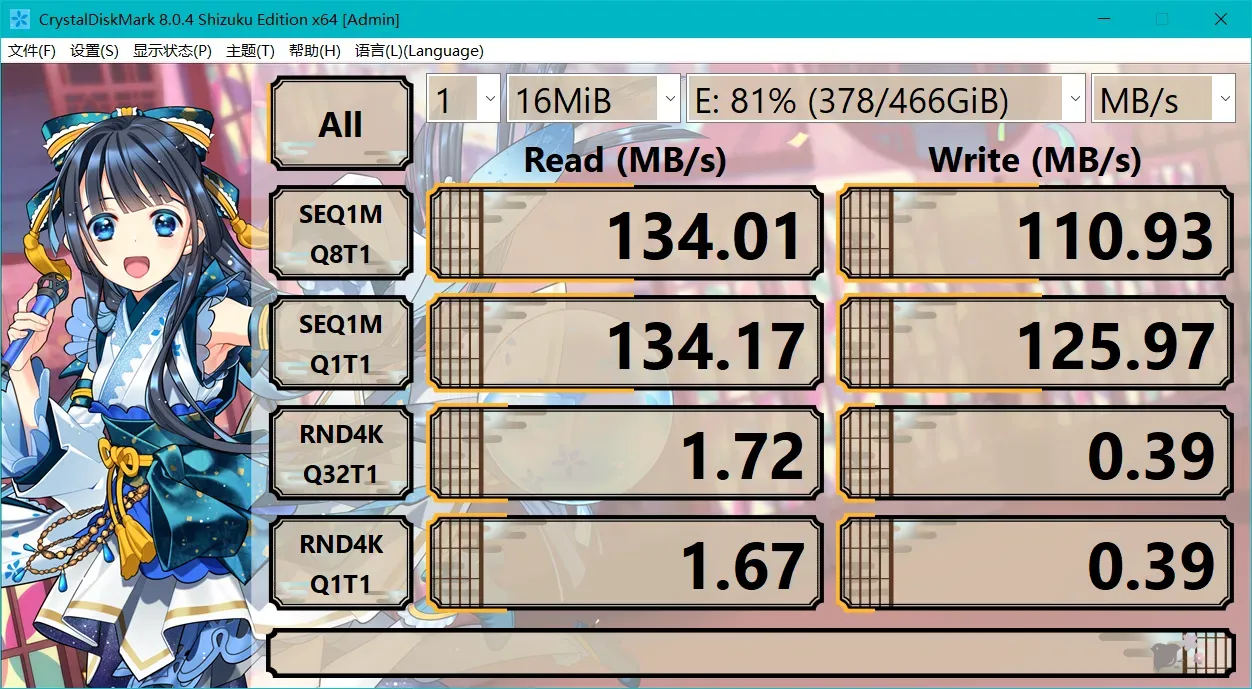

(4)机械硬盘速度测试

使用的机械硬盘读取器的最高速度支持500MB/S

机械硬盘插入拓展坞后显示如下:

使用拓展坞读取机械硬盘的时候(特别是3.5寸的机械硬盘),需要给拓展坞外接供电(下图中白色的线就是外接供电),不让带不动机械硬盘

测试的速度如下:

可以看到最高读取速度为134MB/S左右,差不多就是机械硬盘的速度了,还行

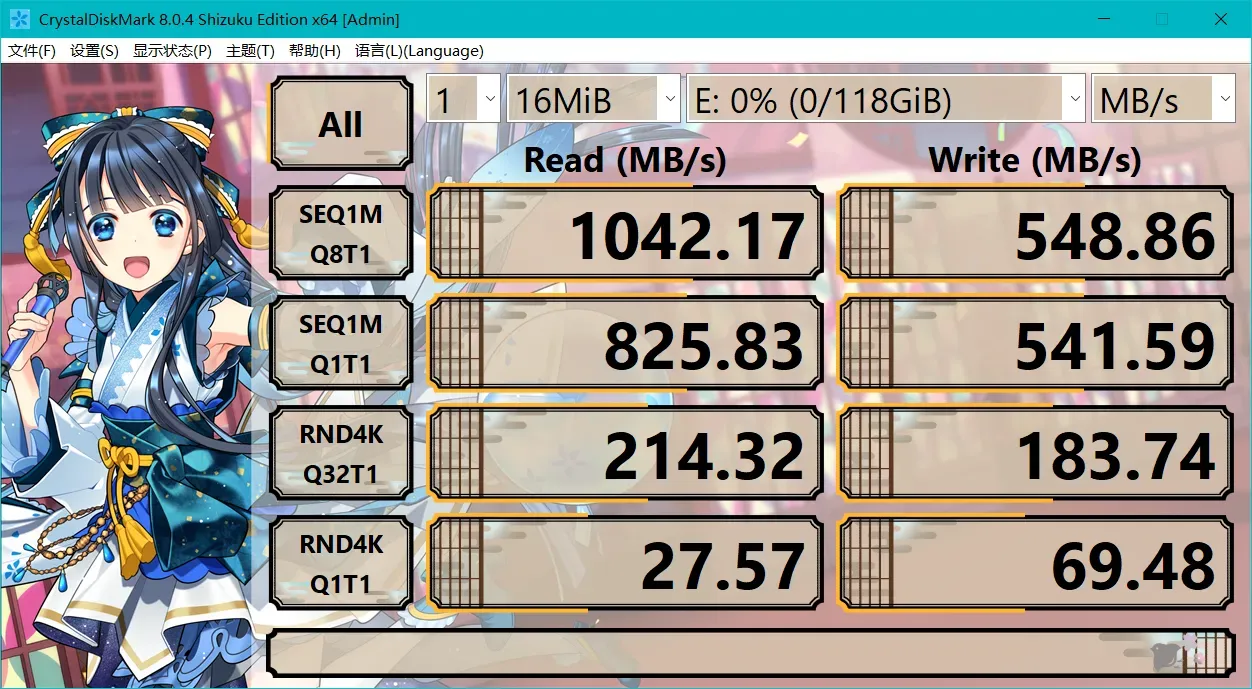

(5)固态硬盘速度测试(拓展坞最高速度测试)

速度测试:

最高读取速度为1042MB/S左右,可以跑到VL822芯片的最高速度,还是不错的

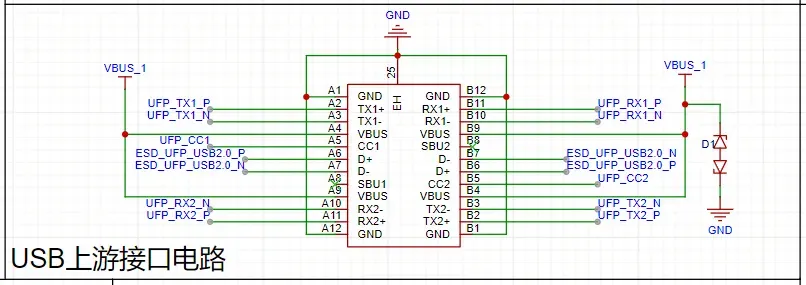

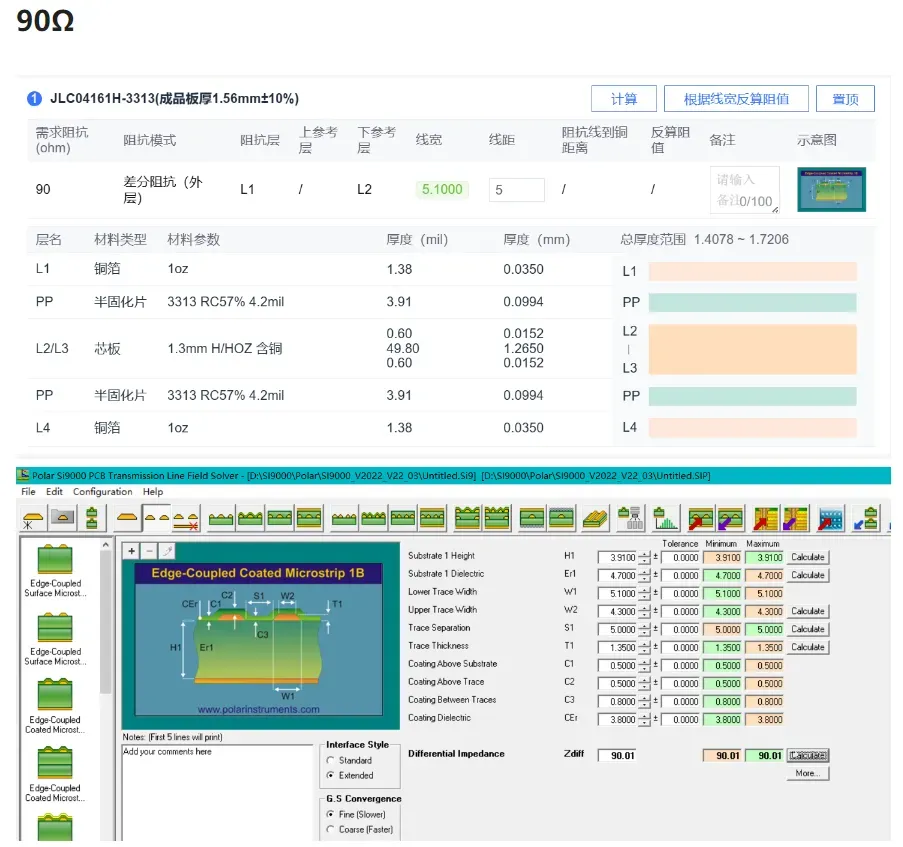

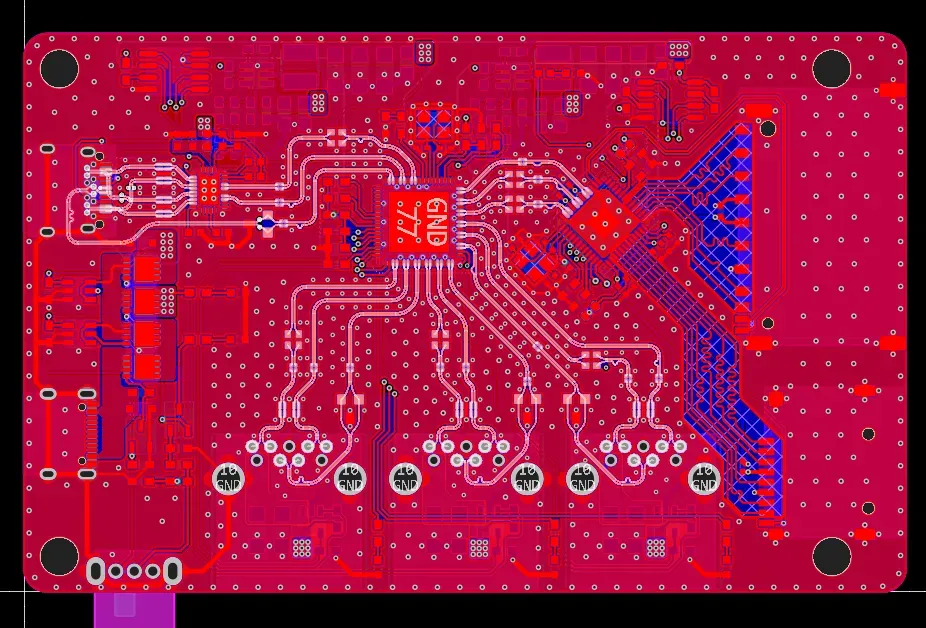

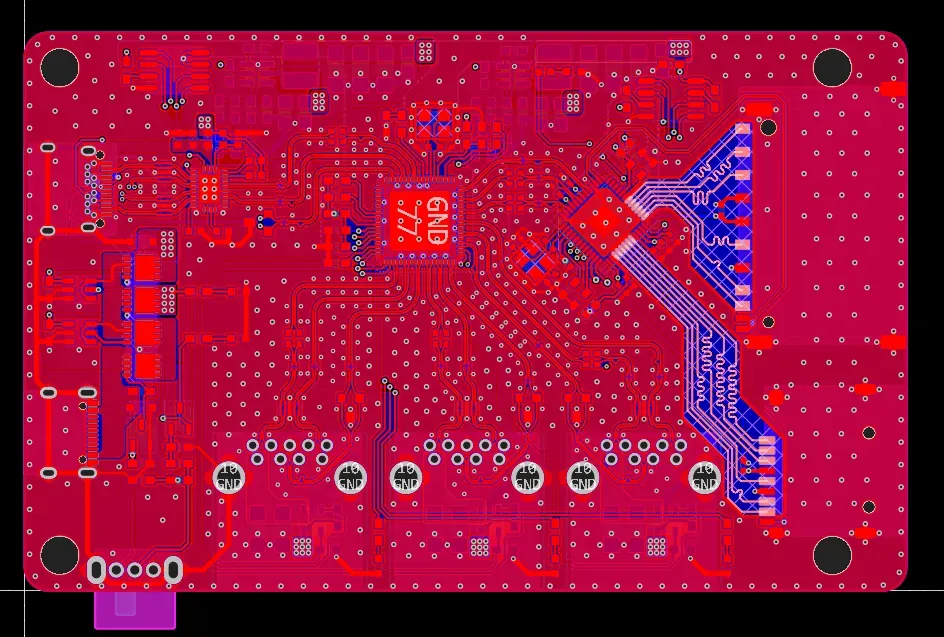

四、阻抗匹配设置

相关设置

1、下图高亮的线为需要做90Ω阻抗的线,正反面都要做阻抗匹配

2、下图高亮的线为需要做50Ω阻抗的线,只有正面需要做

设计图

未生成预览图,请在编辑器重新保存一次

未生成预览图,请在编辑器重新保存一次BOM

暂无BOM

暂无BOM 克隆工程

克隆工程工程成员

知识产权声明&复刻说明

本项目为开源硬件项目,其相关的知识产权归创作者所有。创作者在本平台上传该硬件项目仅供平台用户用于学习交流及研究,不包括任何商业性使用,请勿用于商业售卖或其他盈利性的用途;如您认为本项目涉嫌侵犯了您的相关权益,请点击上方“侵权投诉”按钮,我们将按照嘉立创《侵权投诉与申诉规则》进行处理。

请在进行项目复刻时自行验证电路的可行性,并自行辨别该项目是否对您适用。您对复刻项目的任何后果负责,无论何种情况,本平台将不对您在复刻项目时,遇到的任何因开源项目电路设计问题所导致的直接、间接等损害负责。

评论