表贴网口座2.5G以太网RTL8156BG芯片USB3.0网桥

简介

使用RTL8156BG-CG芯片的USB3.0接口2.5G以太网桥的表贴RJ45母座版本 需提前准备双公USB3.0直通线,或修改电路

简介:使用RTL8156BG-CG芯片的USB3.0接口2.5G以太网桥的表贴RJ45母座版本 需提前准备双公USB3.0直通线,或修改电路开源协议

:GPL 3.0

描述

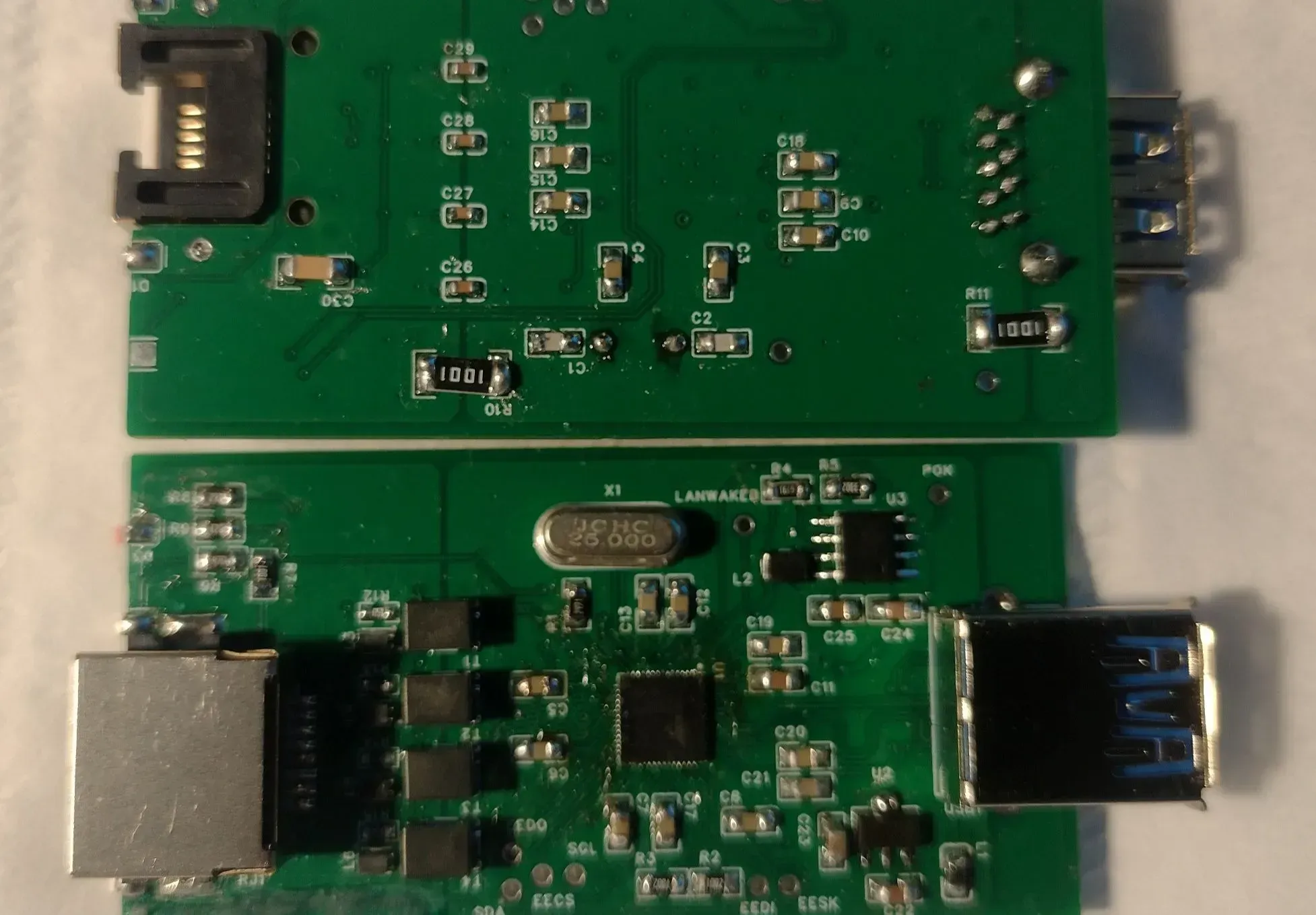

本项目照比 分立变压器2.5G以太网RTL8156BG芯片USB3.0网桥 变化不大,也可以说本项目是之前项目的表贴RJ45版本

开口朝下的RJ45连接器价格是较为昂贵的,而表贴RJ45价格要低廉许多,刚好和大部分以太网芯片接口是同向的,不需要翻到背面去。

众所周知,高频信号吃不消过孔引入的干扰,我要是把所有的插针器件全换成表贴的,那还不性能爆炸,2.5G直接冲到3G。

我瞎说的,

毕竟,

"想用表贴RJ45做一个基于RTL8372的交换机,调整RJ45沉板的开口尺寸费了半天劲,再回头画原理图结果连个RTL8372的手册都找不到。一阵无能狂怒以后,索性拿之前的板子改了一个。"这事,

不能跟外人说。

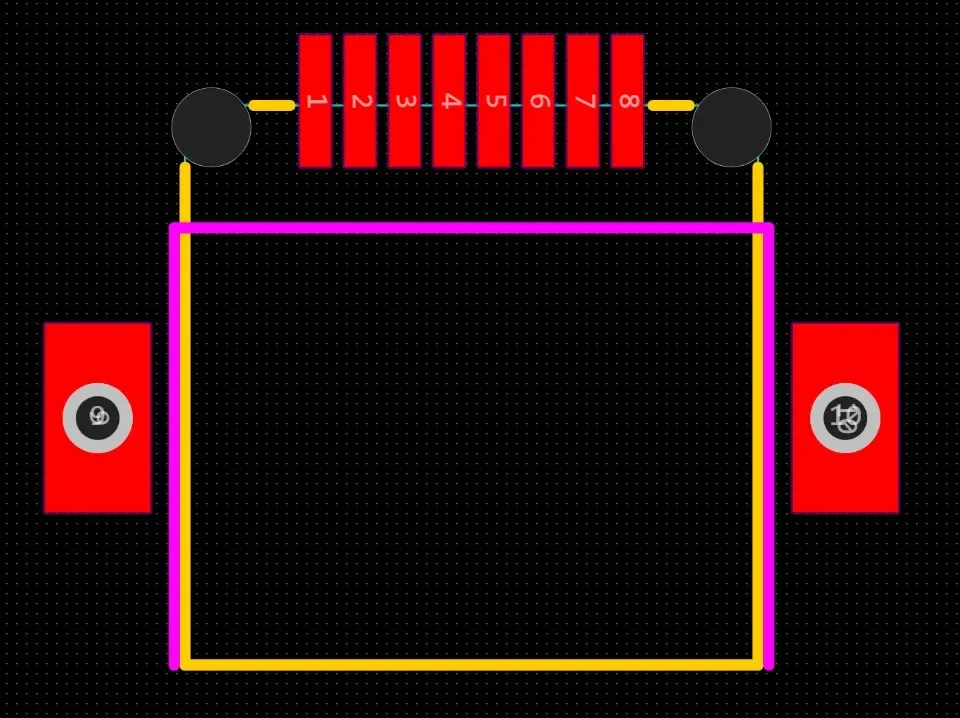

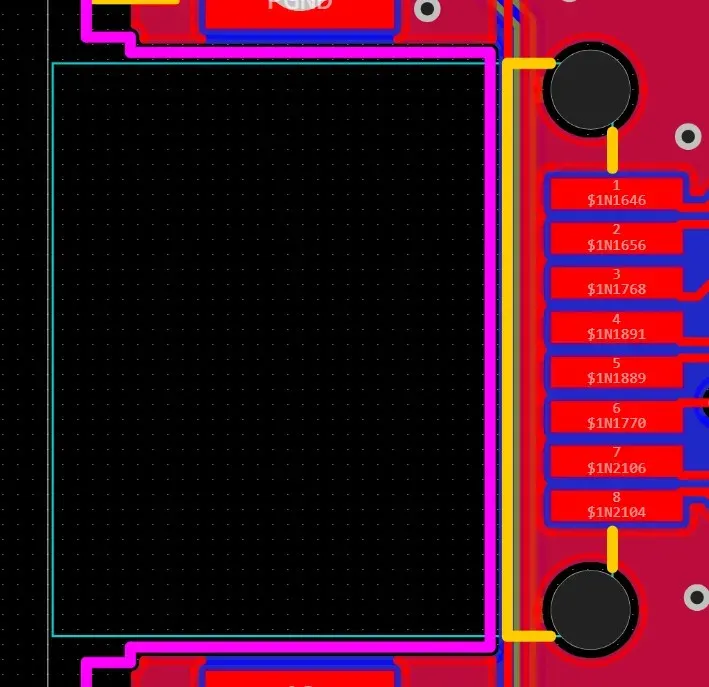

带外壳RJ45沉板表贴连接器的封装,用lceda的默认封装,是放不进去的。

因为在前端,有一点包着的外壳,就突出来了,塞不进上图中方形的半槽,所以需要开口前端或整体加宽。

板子来到以后,要修剪老半天才能用。

之后,亡羊补牢把封装修改成上面那样。

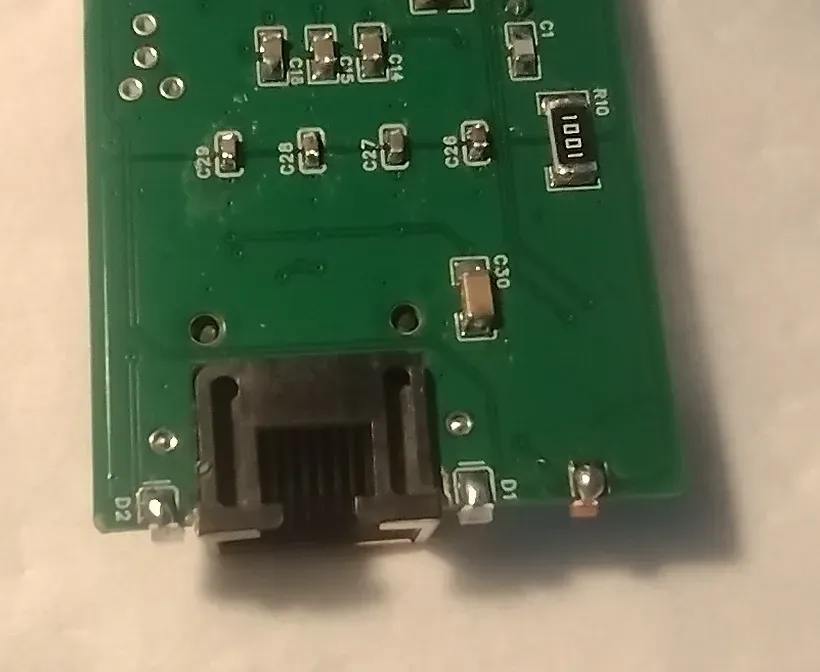

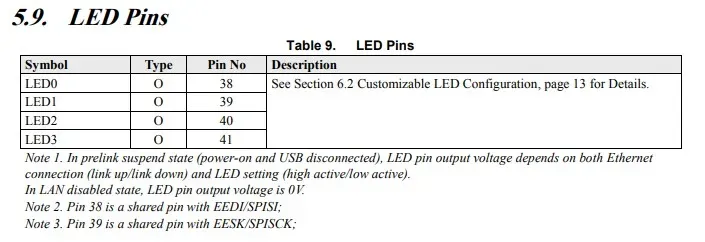

最终成品,垂直焊在板子边上的LED和RJ45正面基本平齐(意义不大)。

经过人工测量并手动加宽开口后,发现RJ45座虽然能塞进去,但塞得有点费力,明显感觉接触的部分是靠弹性挤进去的。

为此,开口加宽的部分又加深10mil,实际焊接完以后可能存在一些缝隙。

关于本项目以太网和USB的差分信号走线,稍微多说几句。

众所周知,间距变化、单端蛇形走线(绕等长)、单端走过孔翻到背面(MDIN1从共模电感出来后连接RJ45的6引脚)之类的的操作会导致阻抗不连续

换而言之,等长和阻抗匹配只能顾一个,两边兼顾实际上是靠阻抗容许的误差。

而且,即使献祭等长,以太网那边MDIN1最终到RJ45的6引脚横竖得打过孔分开走,USB3.0那边首先TX要有耦合电容横竖躲不过去,本项目的USB3.0A母座直通设计还得打过孔换位置。

要想处理好,就指望不上简单的工具了,最起码得是Cadence套件的Signal Integrity工具之类的。

反之索性献祭阻抗匹配,倒能光脚不怕穿鞋的,把等长、等宽安排明白还能等距个八九不离十。

既然如此,嘉立创两个免费的FR4层压结构 JLC04161H-7628 和 JLC04161H-3313 ,其中默认为JLC04161H-7628

线宽8Mil、边缘间距7Mil(中心间距15mil)差分阻抗为99.8177,离以太网的100比较接近,离USB的90差点,但不至于差太离谱

也就是说我其实是算过的,实际走线也是个"不至于差太多"的走线。

在此基础之上,我推测这样走线应该能满足一般带宽的要求,所以想找一找这样走线的极限在哪里。

所以,仍然是:

如果本项目的内容能派上用场,又不能接受肤浅处理差分信号对的话,建议自行匹配阻抗。

然后关于设计的部分

如果之前看过 分立变压器2.5G以太网RTL8156BG芯片USB3.0网桥 ,就不用看了,除了RJ45和LED剩下都复制的,没有添加新内容。

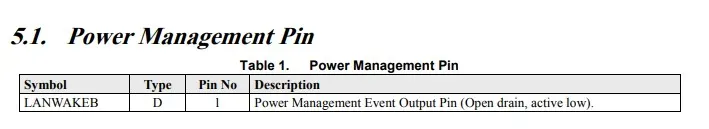

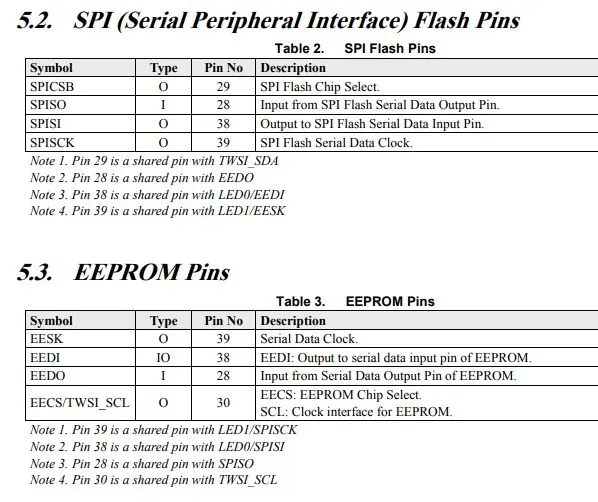

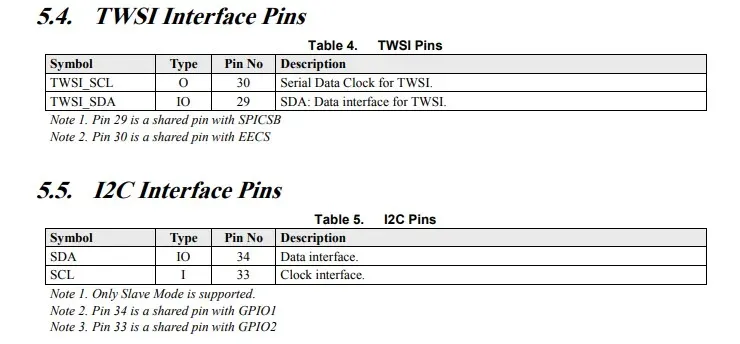

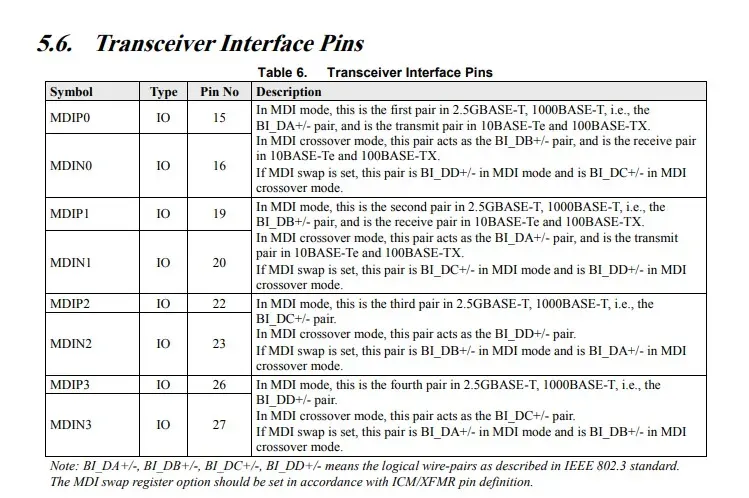

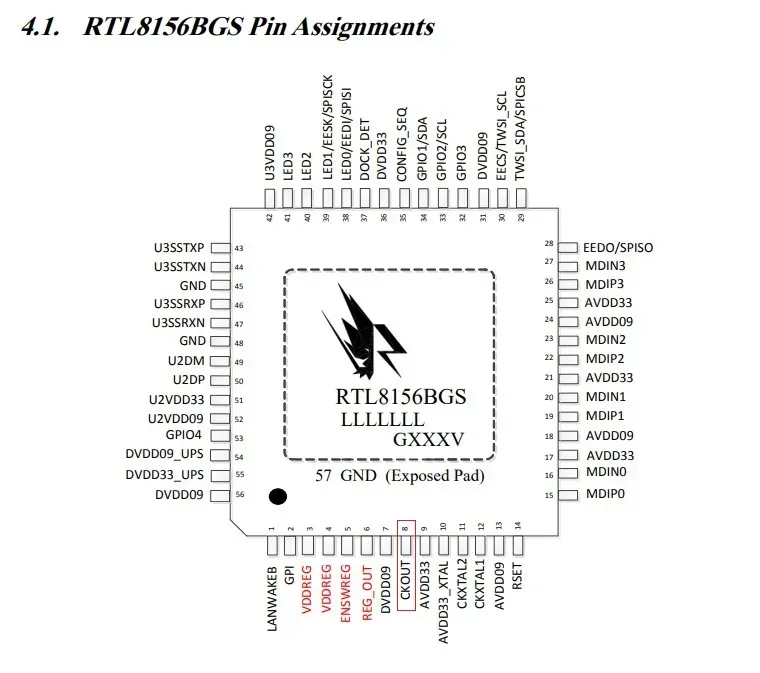

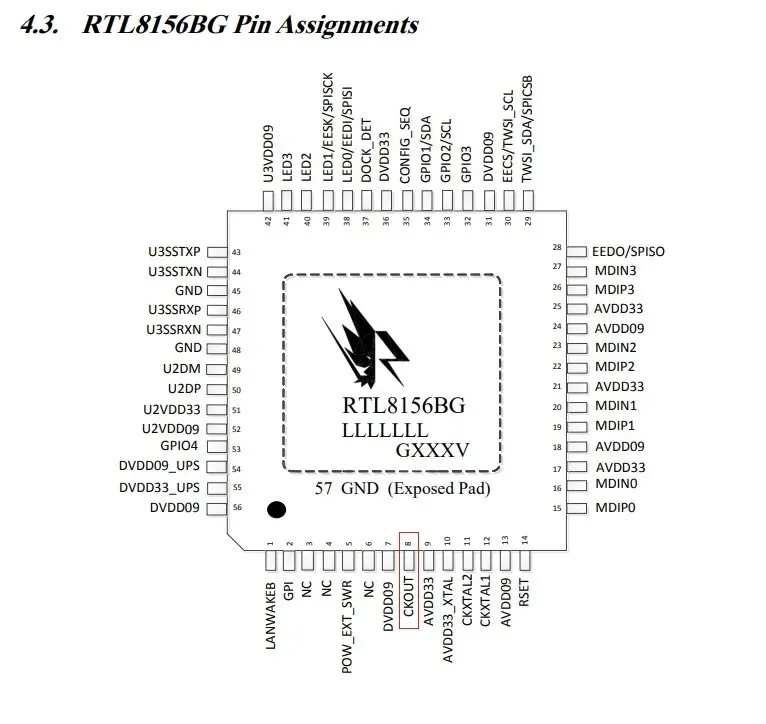

按照手册的引脚说明

LANWAKEB,归类为电源管理引脚却是个开漏输出,功能是指示电源管理事件。引个焊盘出来就行了,不用纠结。

然后通讯接口,或者说配置数据接口,用于上电时与存储芯片通讯,然后把里面的数据送到寄存器并改变RTL8156一部分功能。

这些引脚都是高度复用的,除了第29引脚TWSI_SDA/SPICSB以外,我都引出来一个焊盘,但有一说一,除了39引脚LED1/EESK/SPISCK,如果能搞到10M以太网设备再加上38引脚LED0/EEDI/SPISI,这些全都用不到。

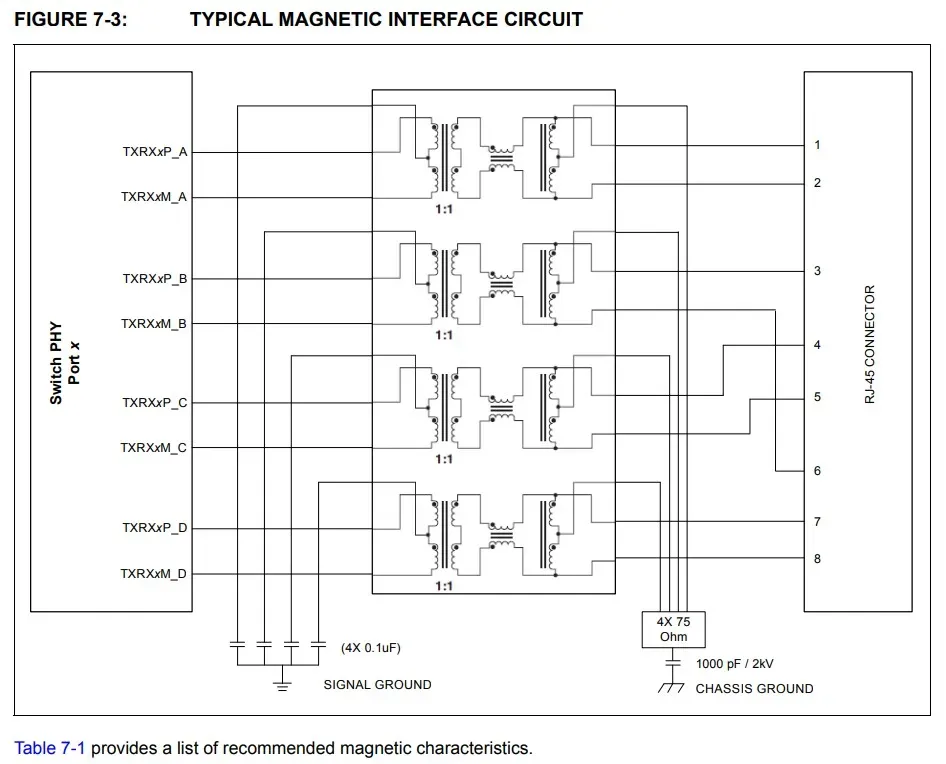

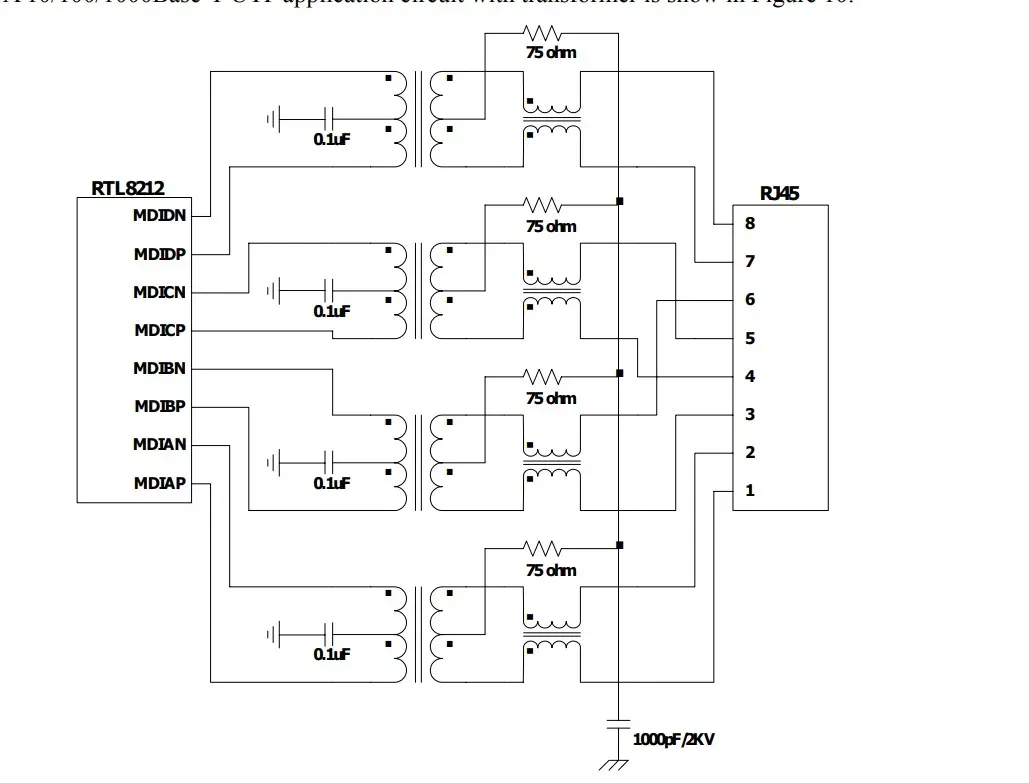

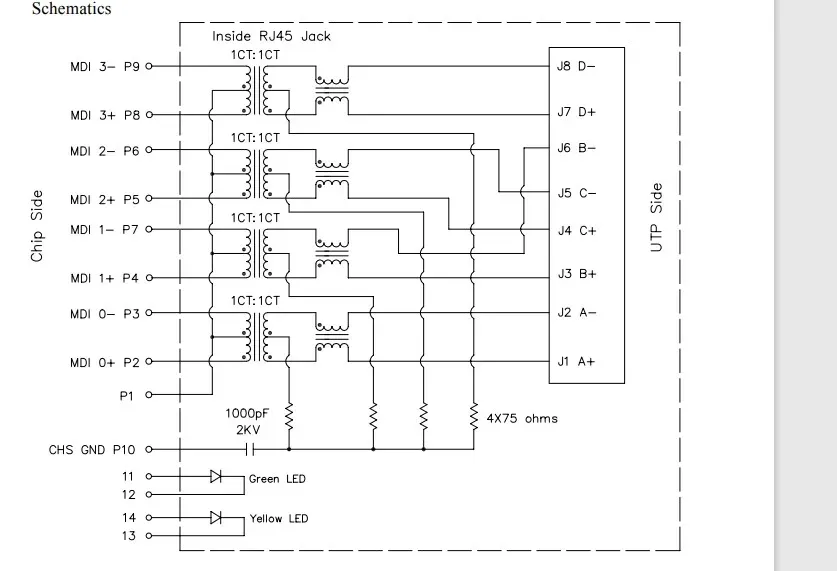

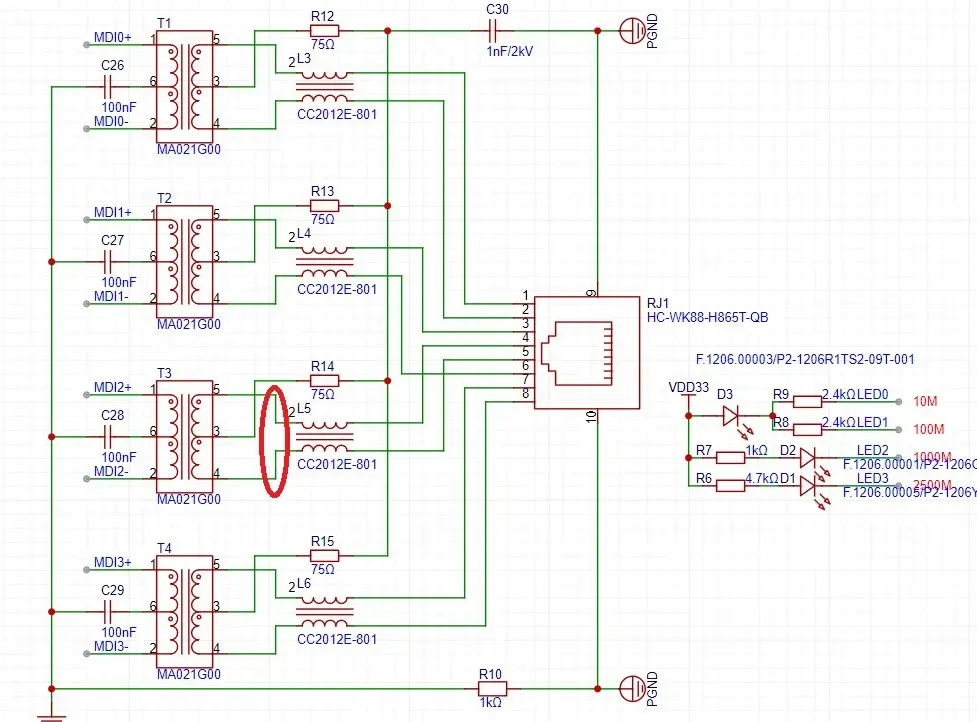

内置PHY的以太网接口,我们要在这里连上以太网分立磁性器件电路,4个脉冲变压器,4个共模电感,4个75欧姆电阻,4个100纳法电容和一个1纳法耐两千伏电容加RJ45座。

再次提醒,

带外壳RJ45沉板表贴连接器的封装,用LCED的默认封装,是放不进去的。

需要在开口处加宽

本项目的太网分立磁性器件电路,是典型的有变压器以太网方案。

如下图

用过911130RJ45模块的,应该记得:

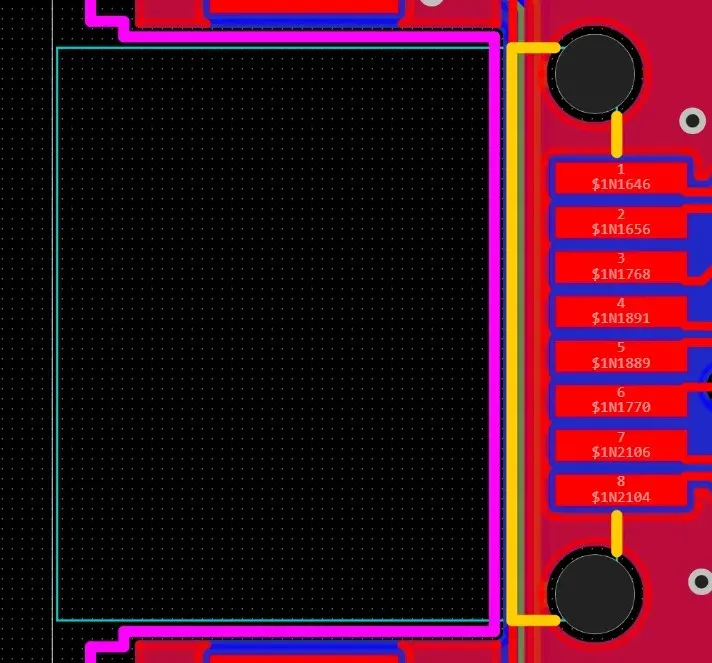

RJ45连接共模电感,共模电感另一端连接脉冲变压器,脉冲变压器再到以太网芯片PHY接口

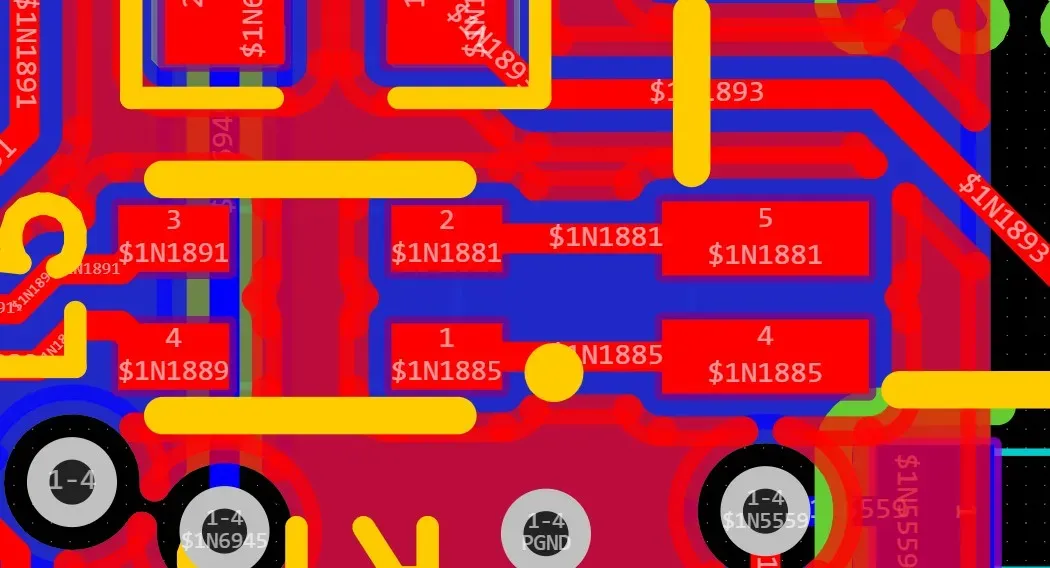

本项目采用MA021G00脉冲变压器,变压器两头引脚间距,和2012(英制0805)的共模电感接近,这就意味着可以直接两边各拉一条直线完成变压器和共模电感的连接。

如下图所式,画圈的是其中一对线中变压器和共模电感的连接,PCB截图是对应的实际连接(正中间两根线)。

相比内置变压器的RJ45模块,需要焊的地方多了不是一星半点儿。

变压器线圈两端电阻大概1.2Ω,两端各接上共模电感一路以后,总电阻大概2Ω出头。

建议焊完以后务必测量一下,不光是为了防止虚焊与连焊,也可能存在损坏的器件。之前就发现过共模电感器件本身短路(4脚之间电阻皆为0),不知道是不是线圈线皮融化导致全连到一起了,也发现过脉冲变压器其中一边两端电阻只有0.5Ω多点,但同时还各自与中心抽头保有0.5到0.6Ω阻值,同样具体原因不明。

众所周知原装器件在编带里都是好的,但焊完以后脉冲变压器和共模电感可能就变成坏的了,另外脉冲变压器引脚相对脆弱,有可能从外壳脱落。

总而言之,这东西对焊接技术有一定要求,器件本身也不算太皮实。

以太网接口每个差分对如果有任意一处虚焊、连焊或器件损坏,则不能建立通讯。

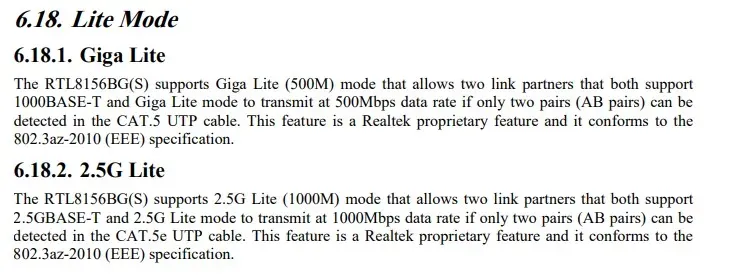

顺带一提,要是运气稍微好点,姑且把MDI1和MDI0两对差分线到rj45处理好了。

瑞昱声称,此时能工作在1000M模式。

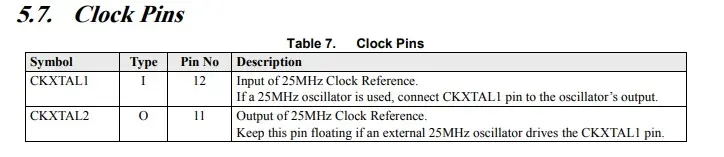

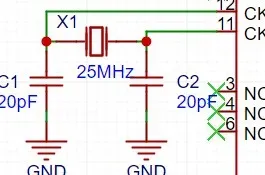

然后是11和12这俩引脚,

接个25M无源晶振,然后带上负载电容,不难。

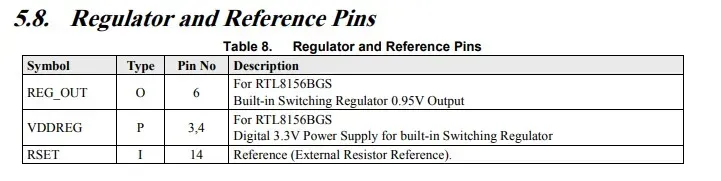

稳压器引脚,仅限带S的芯片,也就是说本项目上的RTL8156BG-CG没有,跳过。

最下面的14引脚RSET,功能是Reference (External Resistor Reference)。

手册上写的是连接一个电阻,连阻值都没有。螃蟹家的芯片见多的,都知道基本上每个以太网芯片都有这么一个引脚,名字可能不一样但都是让接一个电阻还不写阻值。印象中在瑞昱的某个低性能互联网芯片手册中,有个官方参考电路,上面接了2k49的电阻,平时我们看到的同行分享的原理图,都会在此引脚接2k49对地电阻。在一些使用瑞昱芯片的产品拆机照片中,也总能看到一个印着"2491"的电阻。总之这个REST引脚,虽然不知道怎么回事,但就是通过2490欧姆电阻连地。

4个LED引脚,其中LED0和LED1功能复用,手册写了洋洋洒洒一大堆东西,看来看去就会发现上面只是在说:将某个数据写入存储设备的某个地址,就可以把LED定义成什么样。

从头到尾,关于4个LED引脚的默认功能定义,愣是一个字都不写,而且螃蟹家的每个器件都是这样,印象中见过一个写寄存器默认配置的,多少比没有强,其他有一个算一个LED功能让你自己猜。

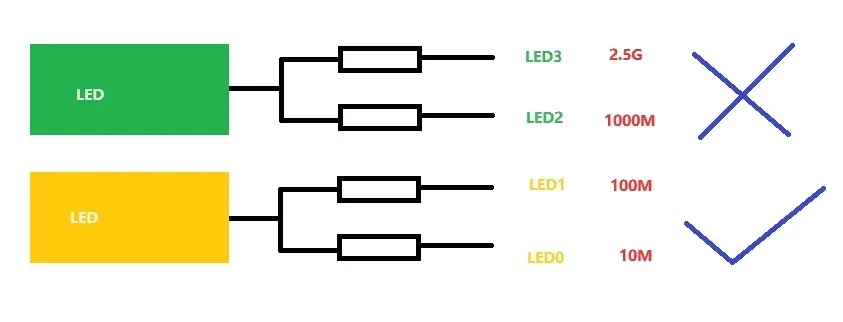

这里我就直接说结论了,

以太网接口连接2.5G网络时,LED3引脚的灯闪烁,

连接1000M网络时,闪烁的是LED2引脚的灯,

连接100M网络时,闪烁的是LED1引脚的灯。

推测要是有10M以太网估计LED0还能闪一个,但没有测试条件。

由于使用的表贴沉板RJ45座不带LED指示灯,只好在外部加几个。

顺带一提,1206的LED在侧面焊起来比较轻松,0805的非常费劲。

另外有一点要注意,LED0和LED1可以各串联电阻连接同一个LED阴极,推断LED0和LED1是开漏输出。

但LED2和LED3应该是推挽输出,同样的接法两个电阻在LED阴极分压导致LED不亮。

所以变成下图这样

由于LED额定电流、亮度等参数不同,串联电阻的值要根据LED参数而定

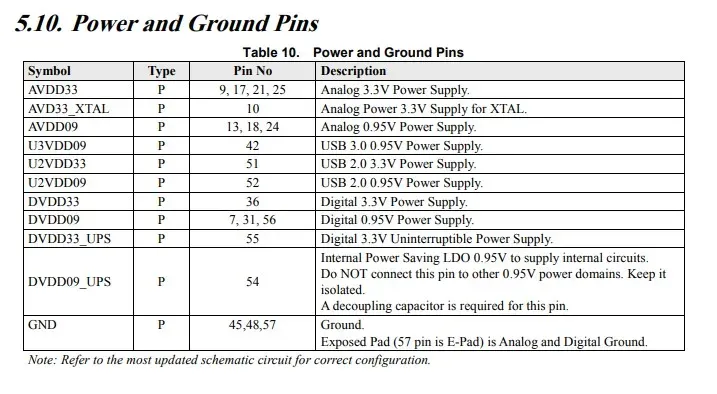

电源的部分

电源引脚分两种电压,3.3V和0.95V。

数字电源和模拟电源可以接到一起,这样只需要从USB总线的5V,获取3.3V和0.95V就可以了

另外要注意,第54引脚DVDD09_UPS不能和其他引脚接到一起。

Internal Power Saving LDO 0.95V to supply internal circuits.

Do NOT connect this pin to other 0.95V power domains. Keep it isolated.

A decoupling capacitor is required for this pin

好在也不需要额外产生一个0.95V给它供电,只需要接个旁路电容就行了,这里选择1μF电容

至于3.3V和0.95V的产生,3.3V好说,毕竟属于很常见的电压。

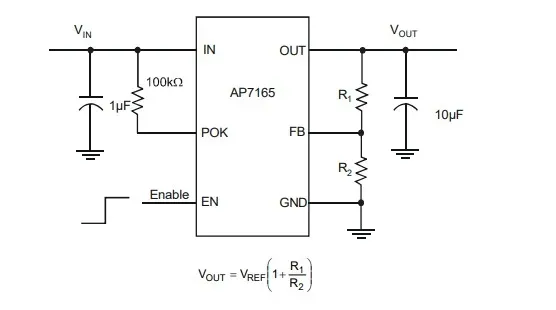

0.95V相对少见,一般没有固定产生0.95V的电源器件,只能找可调压方案。

顺带一提,看到不少人3.3V用稳压器从5V产生,然后0.95V换成了开关电源(DC-DC)甚至又用5V输入。

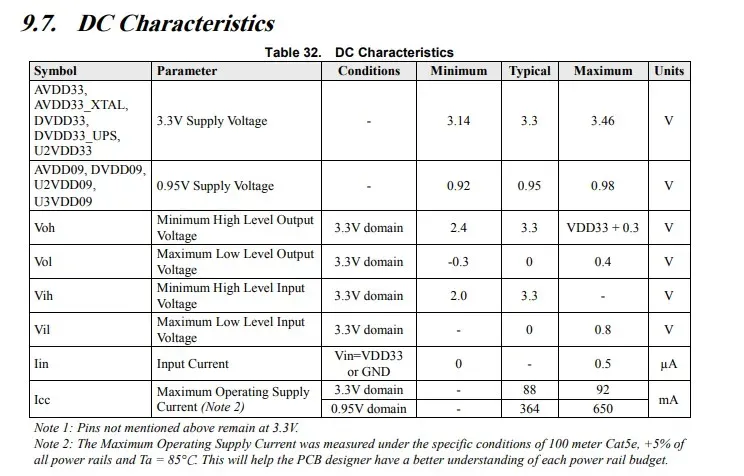

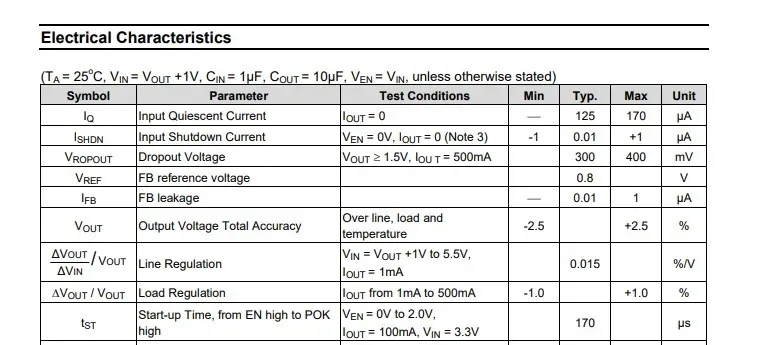

手册上关于电源的参数,注意看表格中最下面两行。

3.3V典型值88mA最大92mA,0.95V典型值364mA最大650mA

3.3V只需要一点点并且要求不高,大头在0.95V那边,工作情况也取决于0.95V的纹波特性。

所以应该用一个3.3V输出稳压器,负担全部92mA+650mA,0.95V从3.3V用稳压器产生。

这样能保证0.95V纹波特性最好,同时也减少对电源滤波电容的依赖。

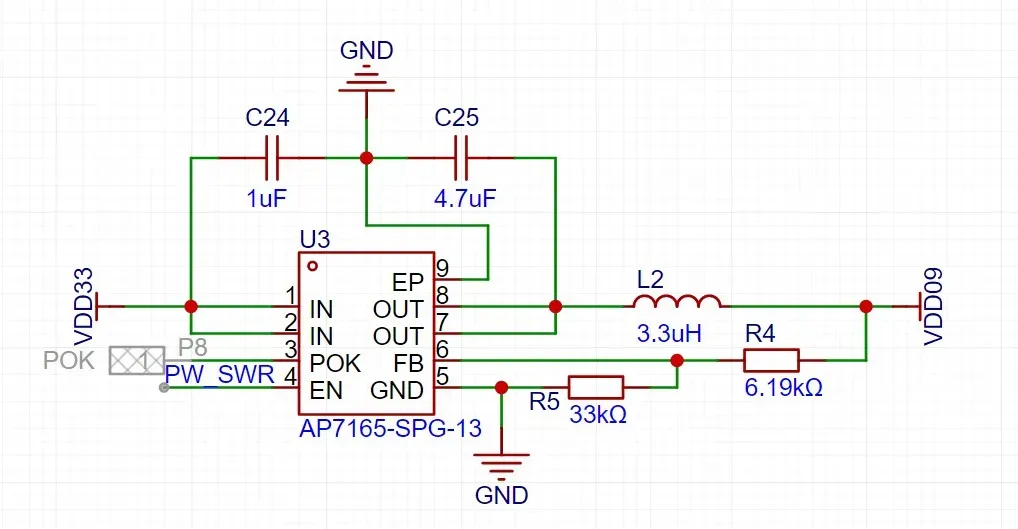

我这边稳压器选用AMS1117-3.3V和AP7165-SPG-13

根据图中公式,代入表格中Vref=0.8计算得出,0.8*(1+6.19/33)=0.95006060606060606060606060606060无限60循环

想把60去掉的话,可以把6.19K换成两个7.5K并联,33K换成20K,也就是0.8*(1+3.75/20)=0.95。

输入连接1117稳压器的3.3V输出,并联1μF旁路电容,输出并联4.7μF旁路电容。

另外我在输出引脚上串联了3.3uH电感一个,希望有效果。

最后是稳压器EN引脚,连接8156BG的5脚POW_EXT_SWR,这是一个输出引脚,用于控制0.95V稳压器输出。

POK的话,悬空应该就可以,我这边也引出来一个焊盘,估计也用不到。

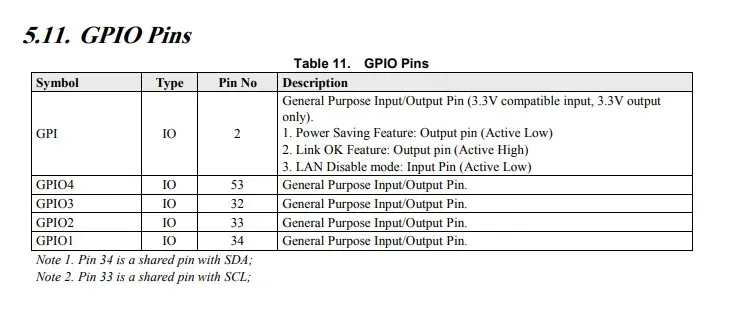

GPIO引脚,除了复用的33和34引脚,我都给他悬空了。

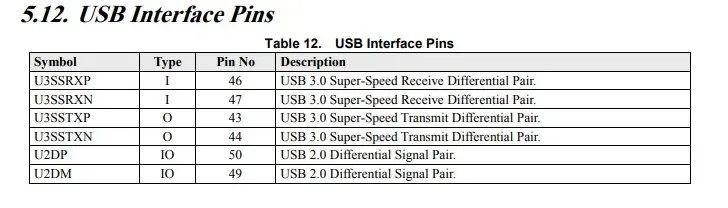

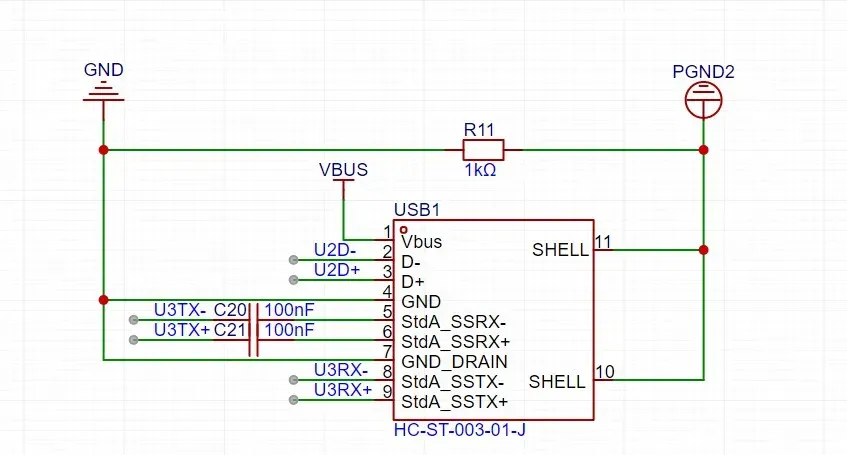

USB接口,连接到USB连接器上。

U2DP/U2DM,U3SSRXP/U3SSRXN,U3SSTXP/U3SSTXN各是一对差分数据线,同样要进行差分布线。

要注意的是,TX差分对需要各串联1个100nF的电容耦合,不串联不一定能工作。

此外USB3.0上行端口与下行端口连接时,SSRX差分对要接到另一端的SSTX差分对,所以SSTX也必然接在另一端的SSRX上

按照标准,此处应该使用USB3.0B母座,3对差分数据线,最好也串联共模电感。

但我的钱包认为应该使用更容易获取USB3.0A母座,共模电感不是必须的。

想来想去,我觉得还是钱包说的有道理,正好手头有几根USB3.0直通双公线

就把RX线接母座TX引脚,TX串联100nF电容接RX脚。

这里提醒正在浏览本项目的朋友,如果有意打样自己试试的话。

记得如果不修改,要搞到一个USB3.0双公直通数据线,而且不能是VBus断开的那种。

还剩下最后几个引脚,其中5脚POW_EXT_SWR连接稳压器EN引脚已经介绍过了,

在RTL8156BGS中5脚会变成输入引脚ENSWREG,用于控制内建稳压器是否生成0.95V,忽略。

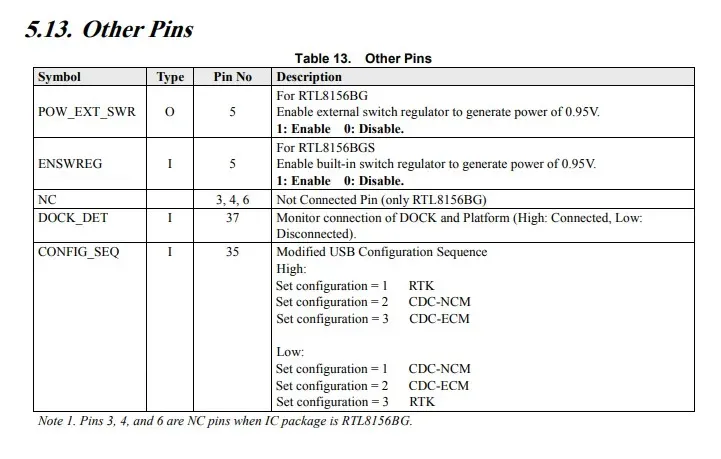

35脚CONFIG_SEQ和37脚DOCK_DET都是配置输入引脚,不知道干啥用的,这俩我都通过10K电阻上拉至3.3V。

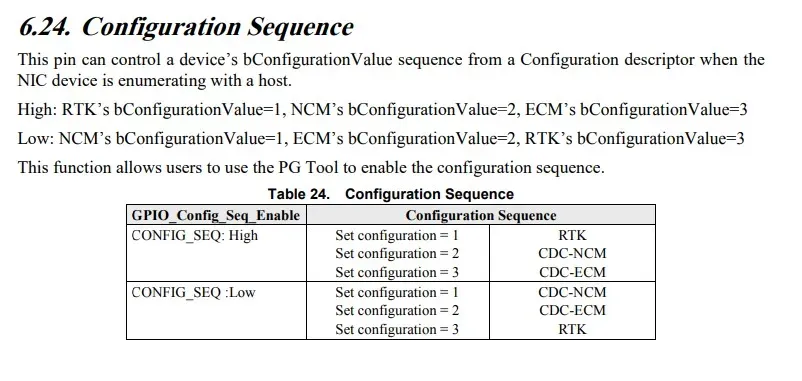

CONFIG_SEQ似乎是配置某些数据的默认含义,如下图。

DOCK_DET用于选择是否监控 DOCK 和 Platform 的连接,高电平有效。

这里细心的朋友就会发现,芯片的第8引脚CKOUT,被手册神隐了。

整个手册有CKOUT的地方,就这俩引脚定义图,别说干什么用的,连是输入还是输出都不知道。

虽然名字带OUT,我猜是输出引脚吧,给它悬空好了。

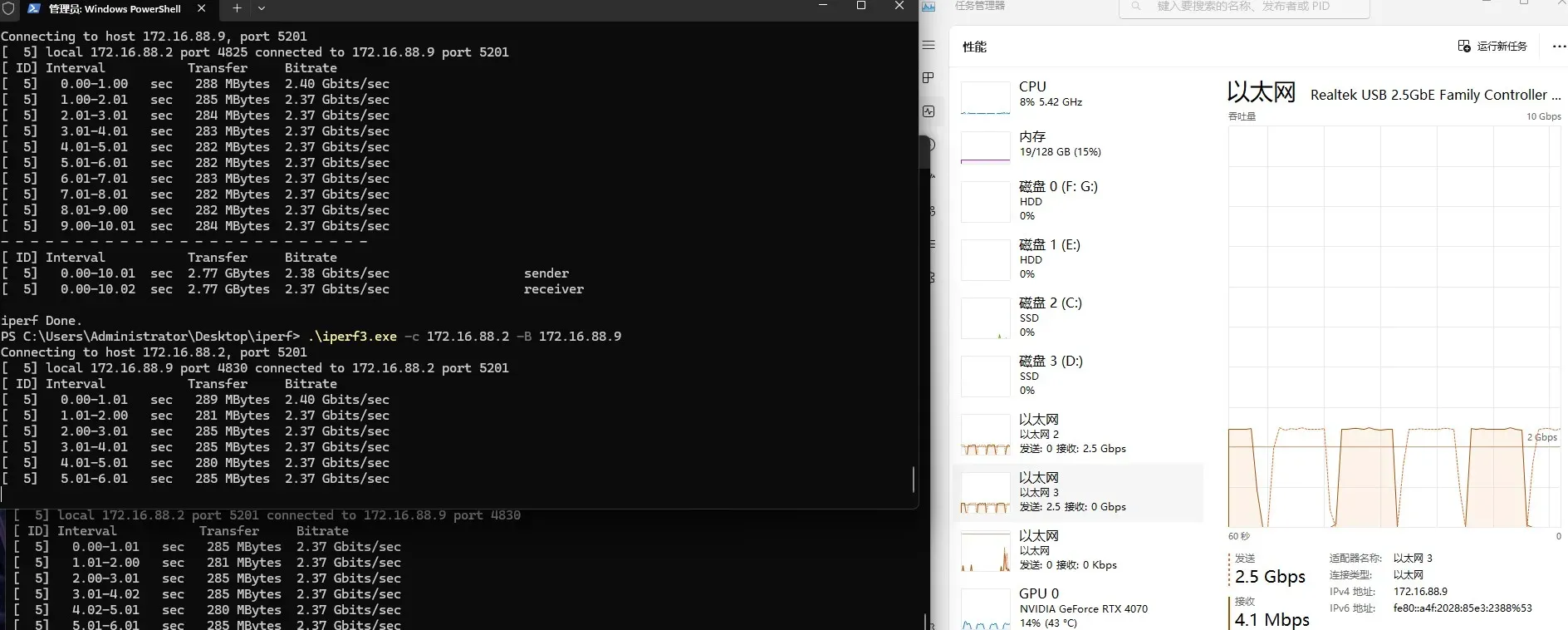

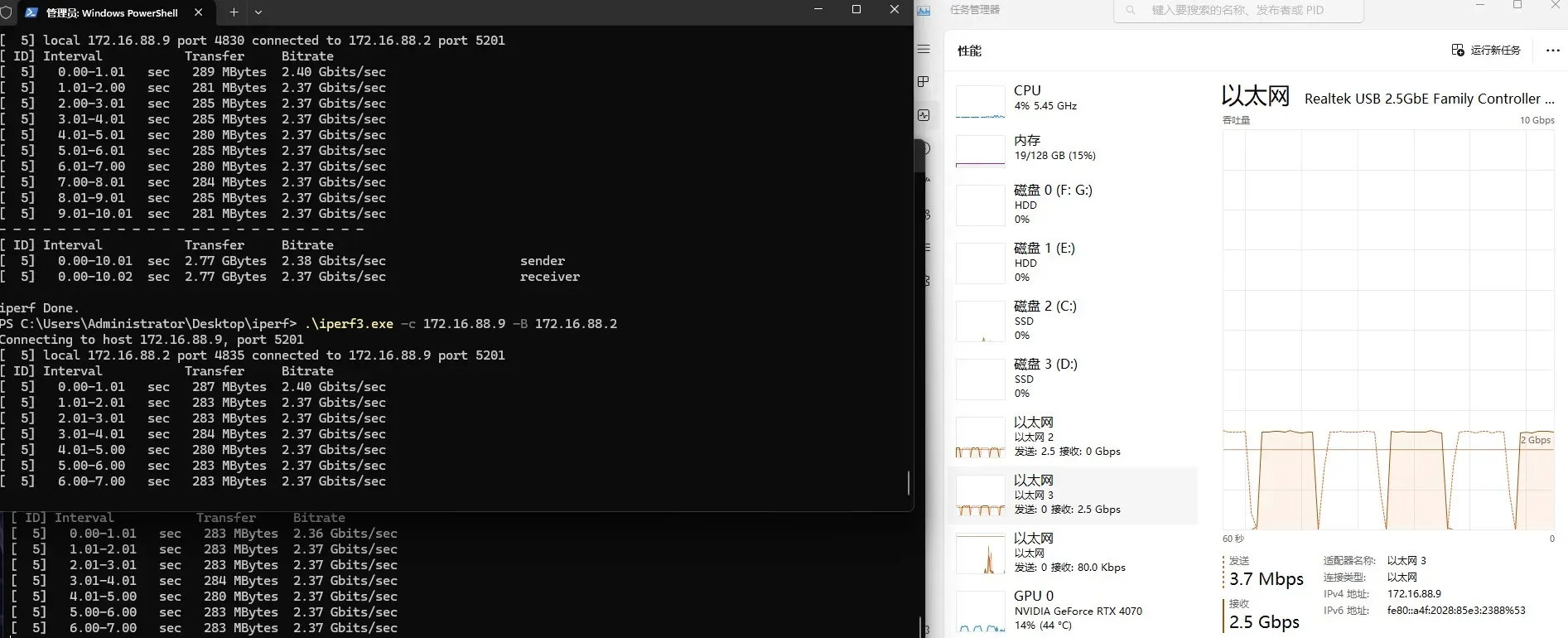

然后又到了实际测试的部分

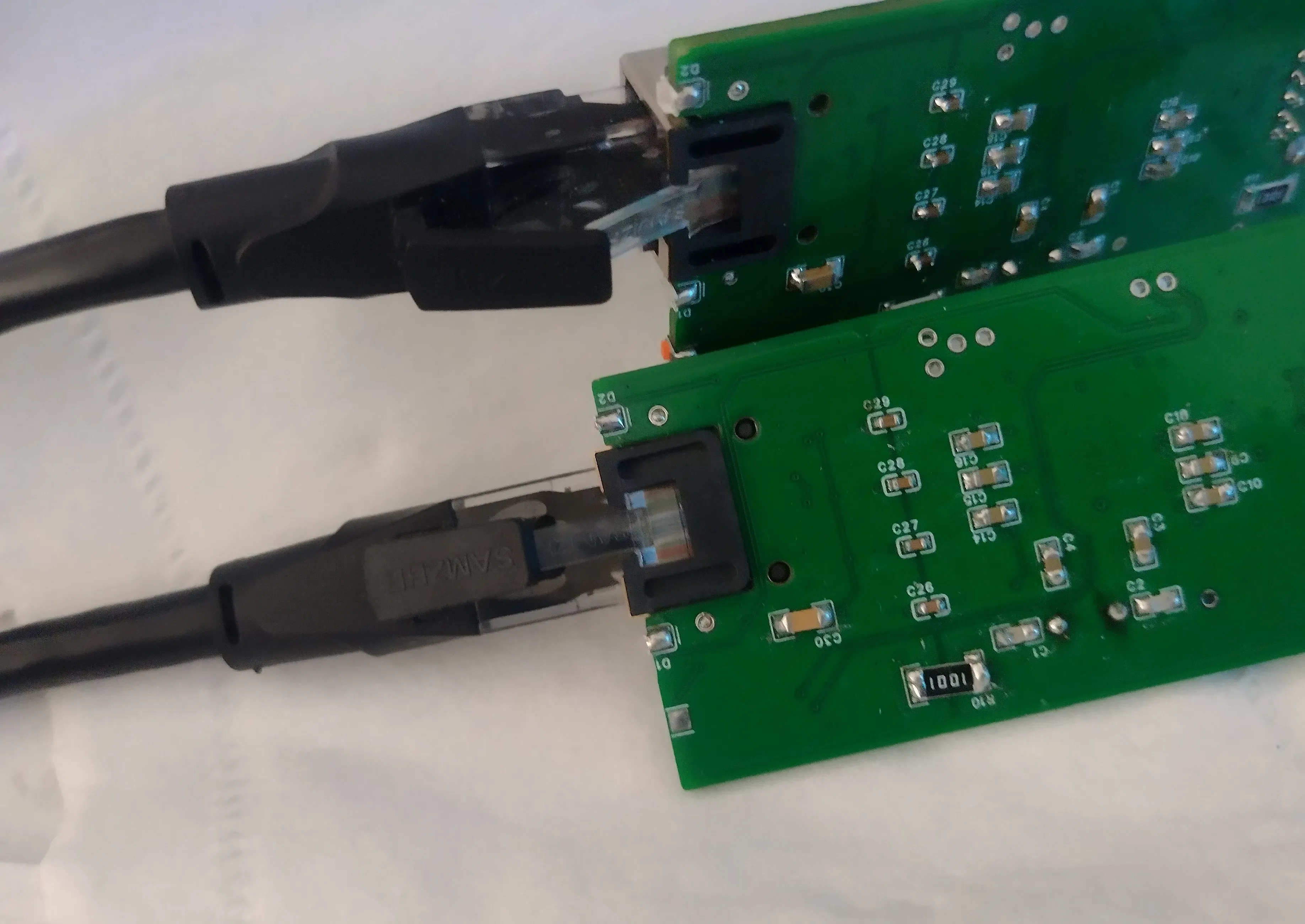

把两个成品用网线连起来

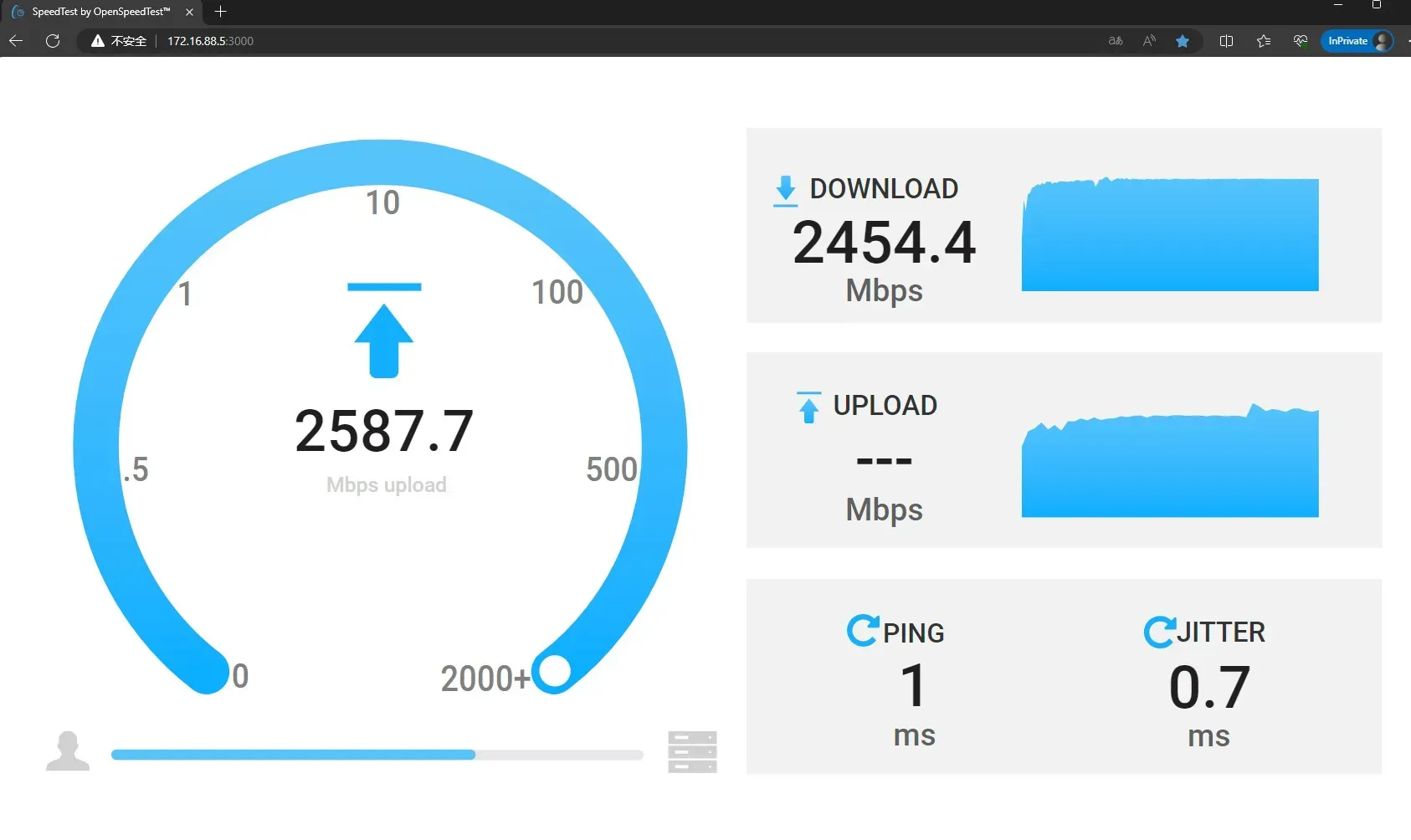

先是iperf3测试,

依旧是神奇的2.37G,当然从任务管理可以看到网卡跑满了2.5G

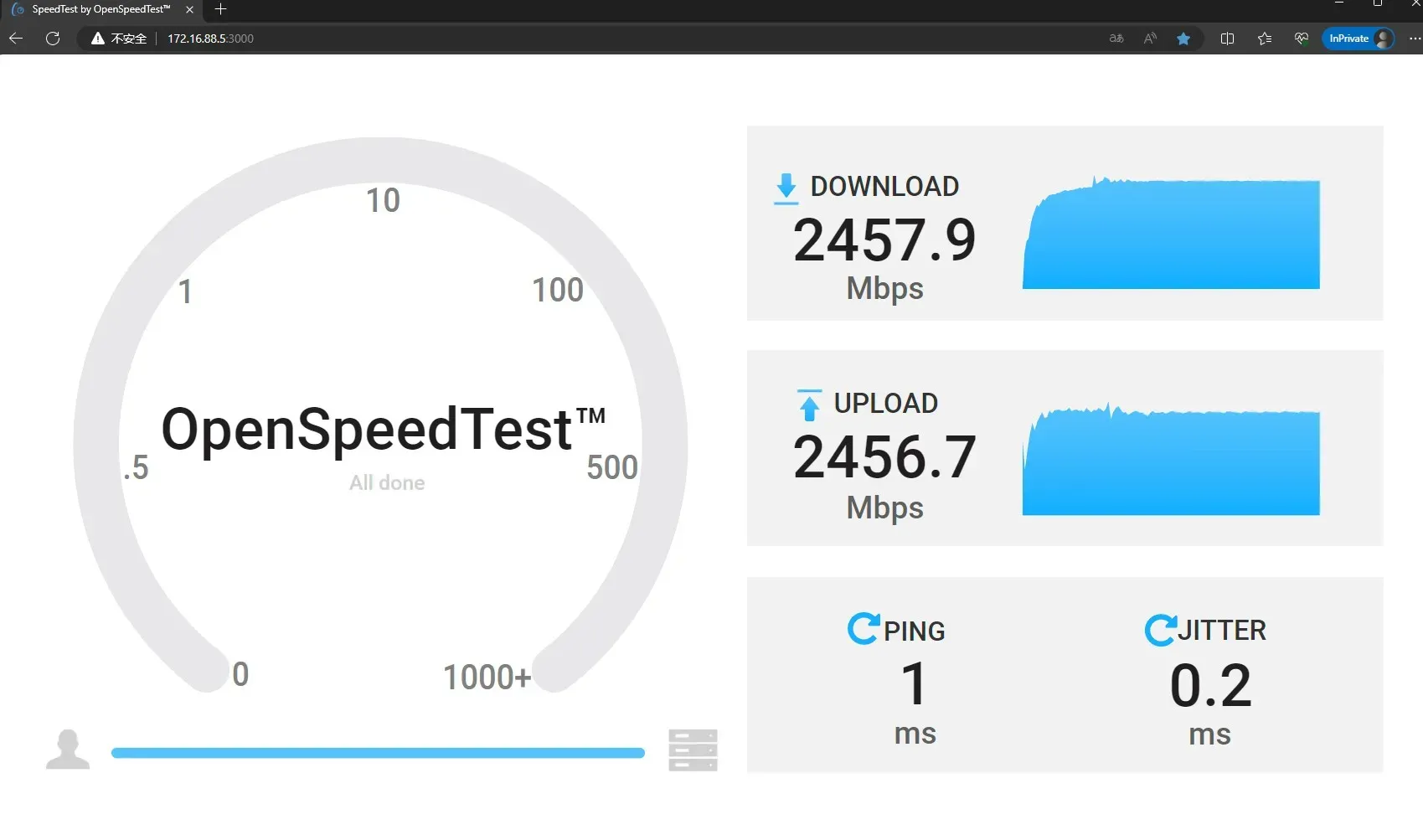

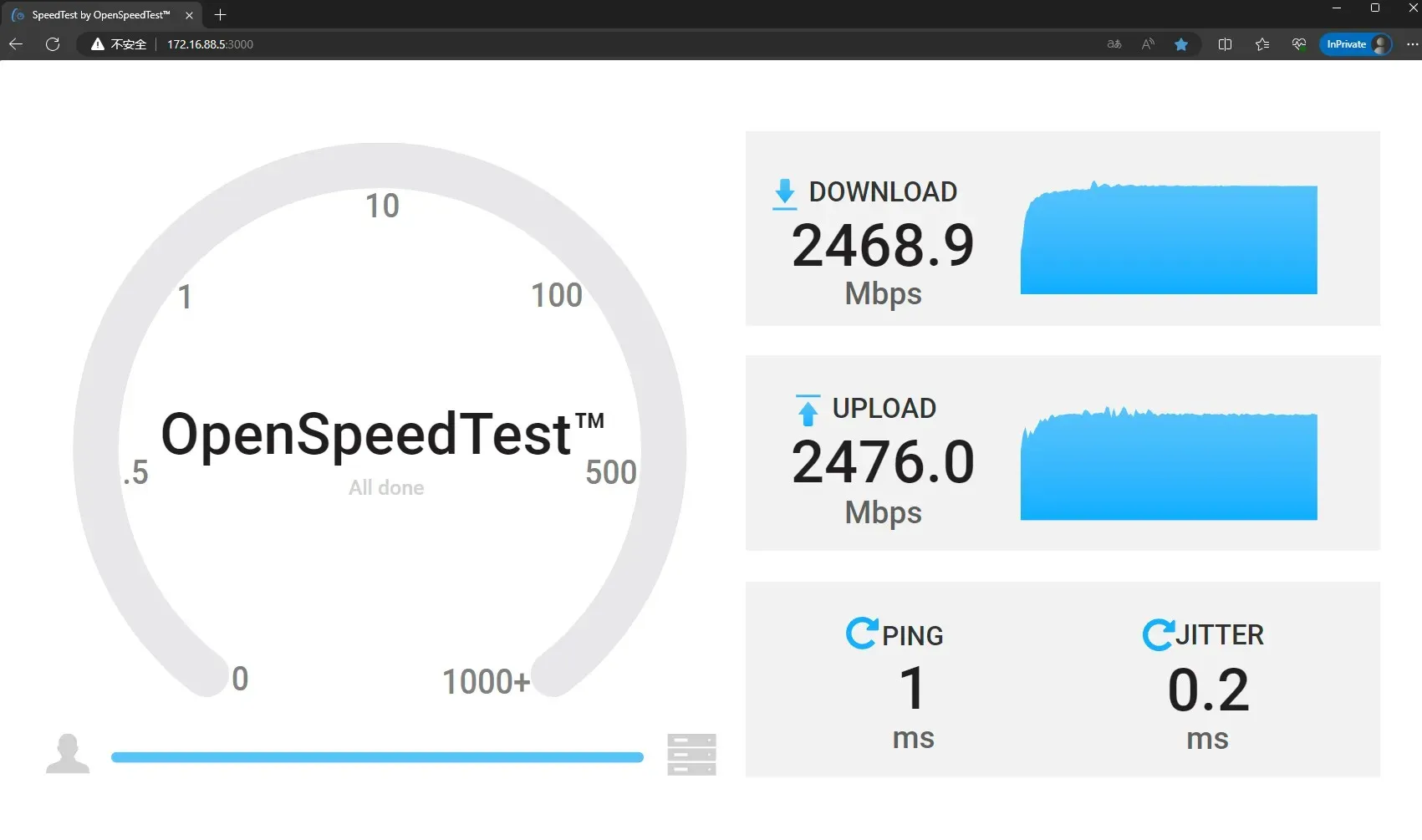

然后是 Free and Open-Source Self-Hosted HTML5 SpeedTest 测试

第一次测试结果

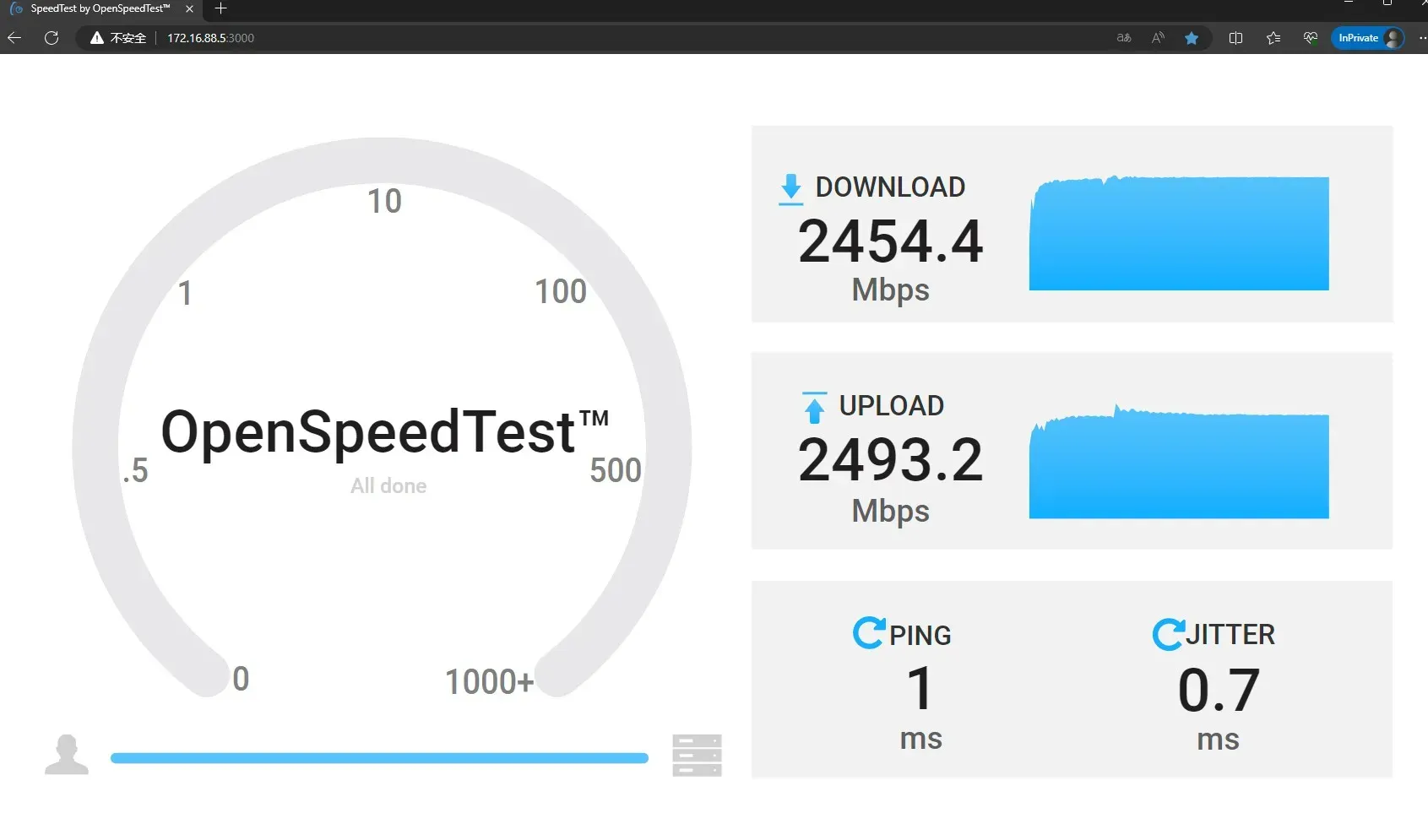

第二次测试结果

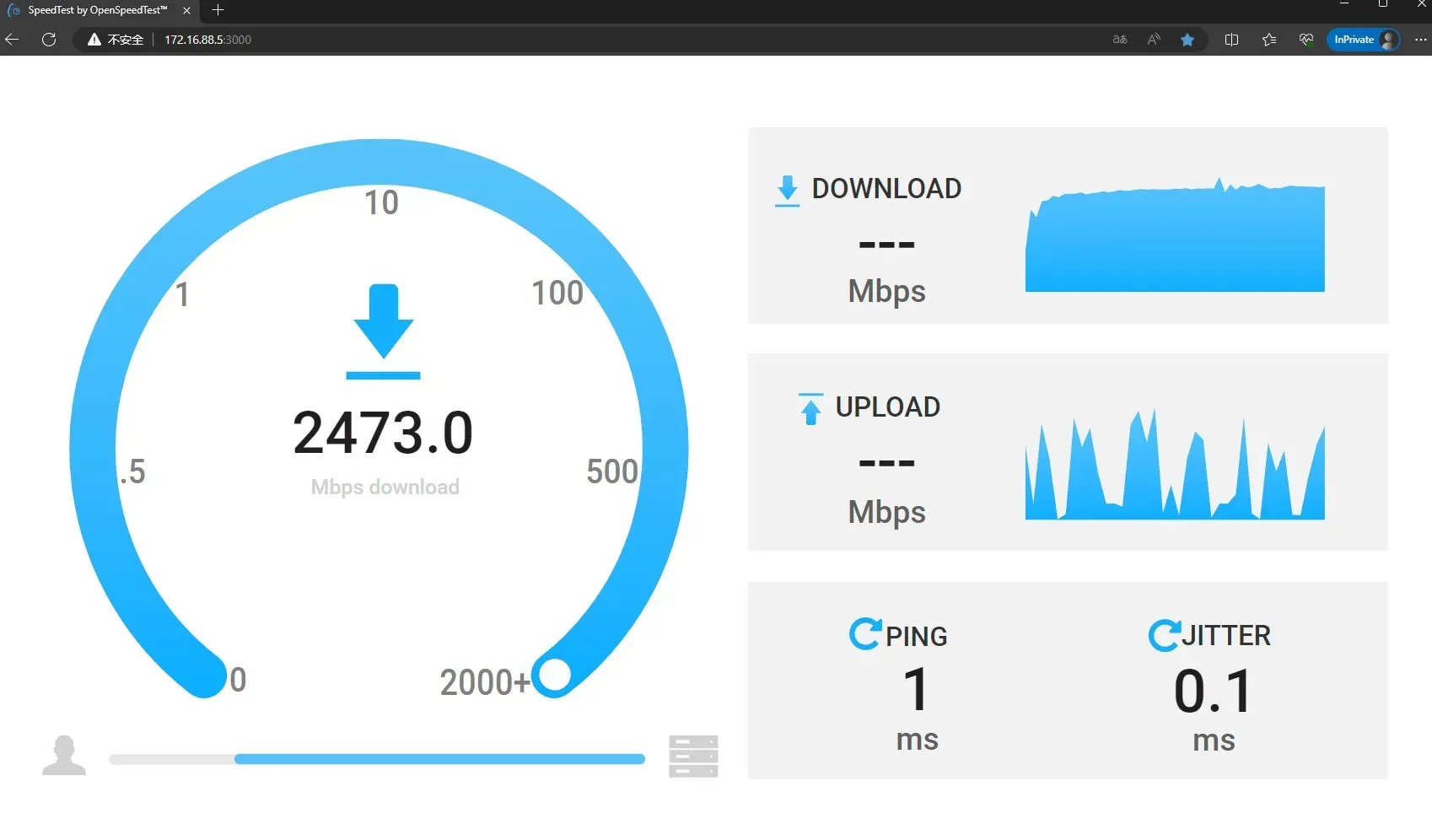

第三次下行测试

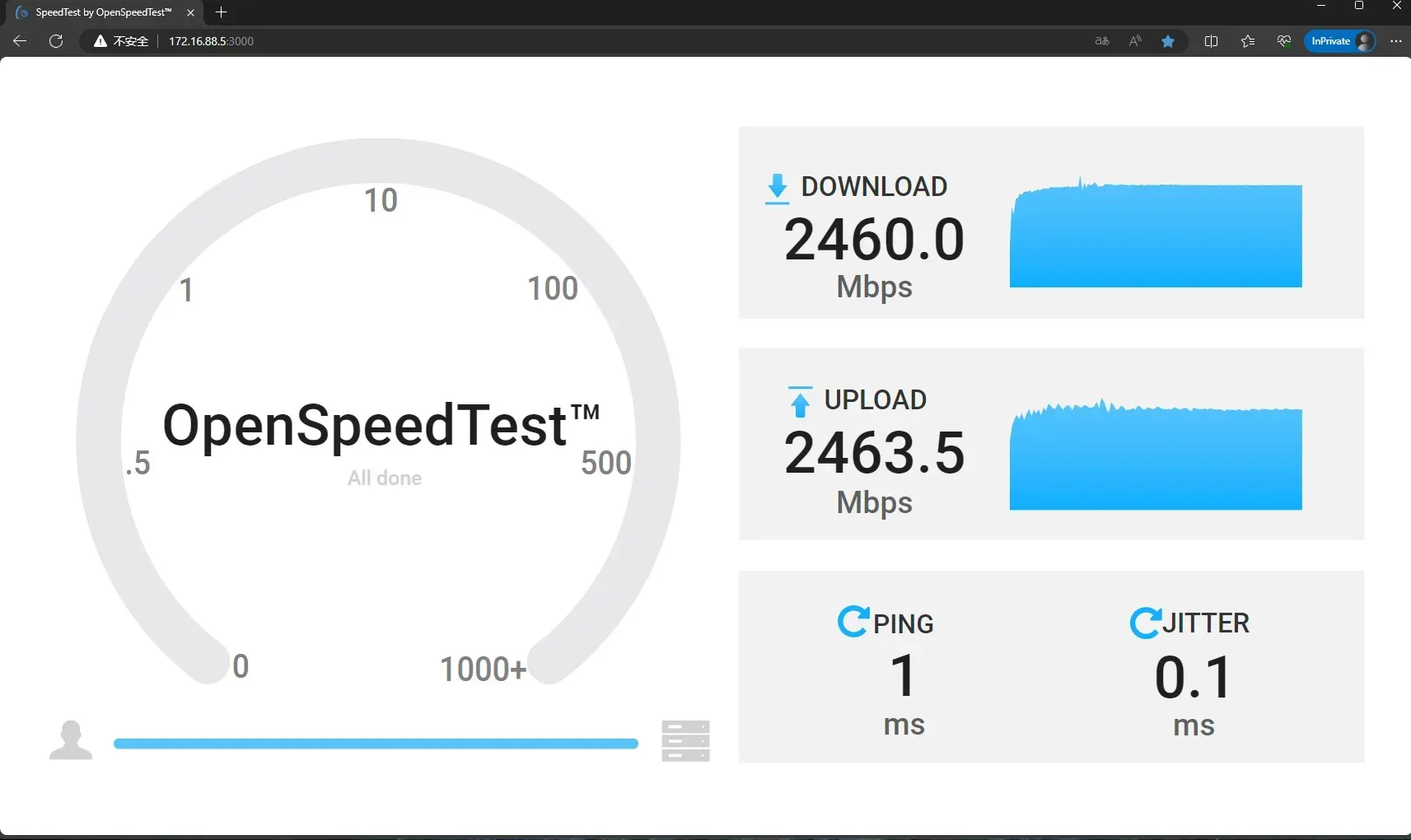

第三次测试结果

第四次下行测试

第四次测试结果

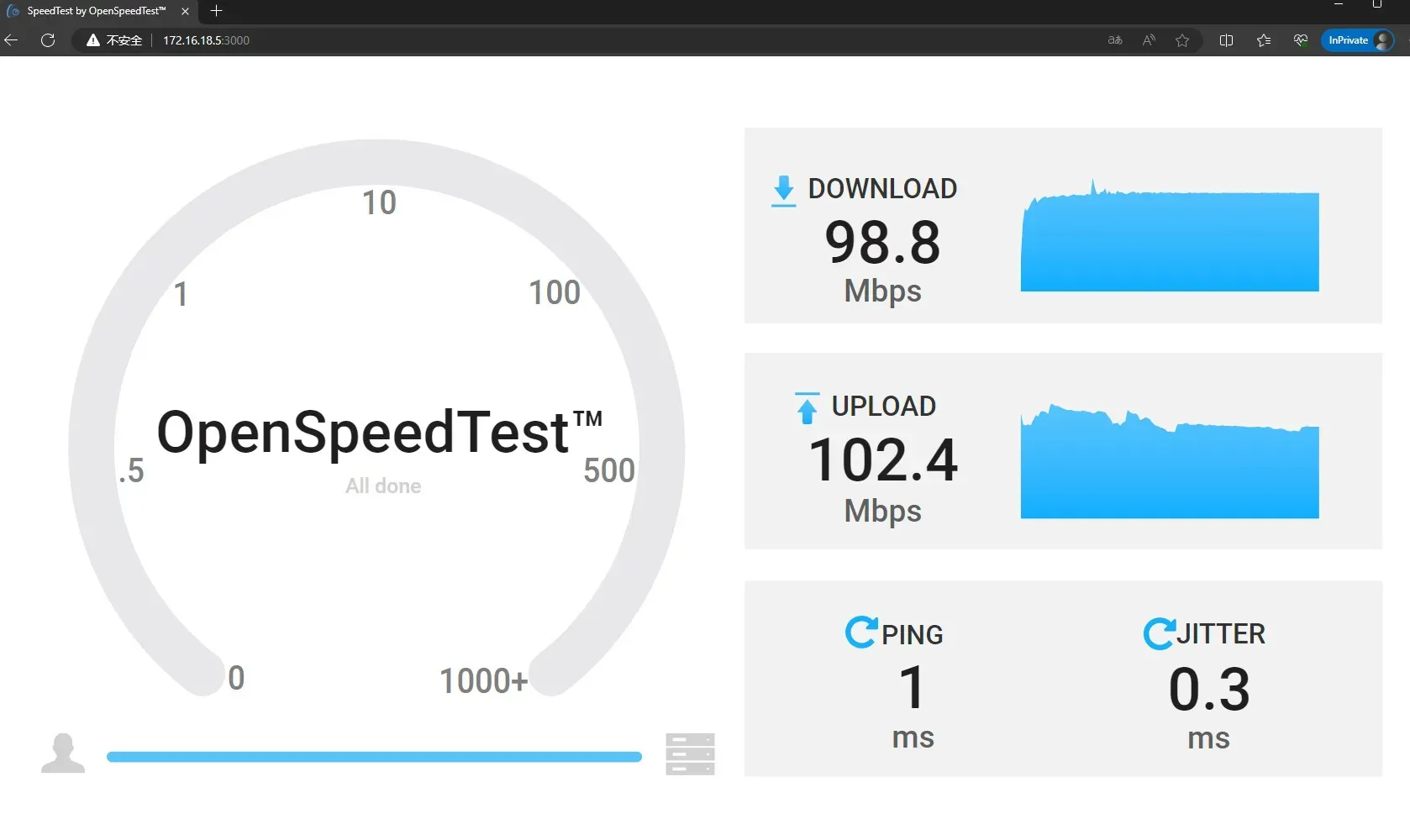

顺带这次跑了一次连接100M以太网时的测试

为什么要跑100M呢?

因为网线坏了,不知道断的哪根线

之前就坏了,现象是偶尔从2.5G掉到1000M

现在彻底坏了,插上以后等老半天协商出1000M(Lite Mode发挥效果,详见手册6.18),偶尔甚至变100M(Lite Mode没发挥效果)

设计图

未生成预览图,请在编辑器重新保存一次

未生成预览图,请在编辑器重新保存一次BOM

暂无BOM

暂无BOM 克隆工程

克隆工程工程成员

知识产权声明&复刻说明

本项目为开源硬件项目,其相关的知识产权归创作者所有。创作者在本平台上传该硬件项目仅供平台用户用于学习交流及研究,不包括任何商业性使用,请勿用于商业售卖或其他盈利性的用途;如您认为本项目涉嫌侵犯了您的相关权益,请点击上方“侵权投诉”按钮,我们将按照嘉立创《侵权投诉与申诉规则》进行处理。

请在进行项目复刻时自行验证电路的可行性,并自行辨别该项目是否对您适用。您对复刻项目的任何后果负责,无论何种情况,本平台将不对您在复刻项目时,遇到的任何因开源项目电路设计问题所导致的直接、间接等损害负责。

评论